# DIGITAL LOGIC & COMPUTER ORGANIZATION (DL&CO)

LECTURE NOTES

II B.Tech (CSE, AI&DS, AI&ML)

**Prepared By**

Mrs. A.SAHITHI

Asst. Prof., Dept. of ECE

#### **Department of**

ELECTRONICS & COMMUNICATIONS ENGINEERING

ANNAMACHARYA INSTITUTE OF TECHNOLOGY & SCIENCES, KADAPA

Utukur (P), C. K. Dinne (V&M), Kadapa, YSR Dist.

#### II Year B.Tech., I Semester

| L | T | P | С |

|---|---|---|---|

| 3 | 0 | 0 | 3 |

### (23HES0402) DIGITAL LOGIC & COMPUTER ORGANIZATION

**Course Objectives:** The main objective of the course is to

- Provide students with a comprehensive understanding of digital logic design principles and computer organization fundamentals

- Describe memory hierarchy concepts

- Explain input/output (I/O) systems and their interaction with the CPU, memory, and peripheral devices

Course Outcomes: After completion of the course, students will be able to

- Differentiate between combinational and sequential circuits based on their characteristics and functionalities. (L2)

- Demonstrate an understanding of computer functional units.(L2)

- Analyze the design and operation of processors, including instruction execution, pipelining, and control unit mechanisms, to comprehend their role in computer systems.(L3)

- Describe memory hierarchy concepts, including cache memory, virtual memory, and secondary storage, and evaluate their impact on system performance and scalability. (L3)

- Explain input/output (I/O) systems and their interaction with the CPU, memory, and peripheral devices, including interrupts, DMA, and I/O mapping techniques. (L3)

- Design Sequential and Combinational Circuits(L6)

#### **UNIT-I:**

**Data Representation:** Binary Numbers, Fixed Point Representation, Floating Point Representation, Number base conversions, Octal and Hexadecimal Numbers, Complements, Signed binary numbers

**Digital Logic Circuits-I:** Basic Logic Functions, Logic gates, universal logic gates, Minimization of Logic expressions. K-Map Simplification, Combinational Circuits, Decoders, Multiplexers

#### IINIT\_II•

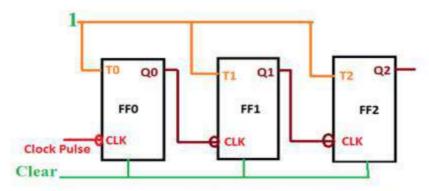

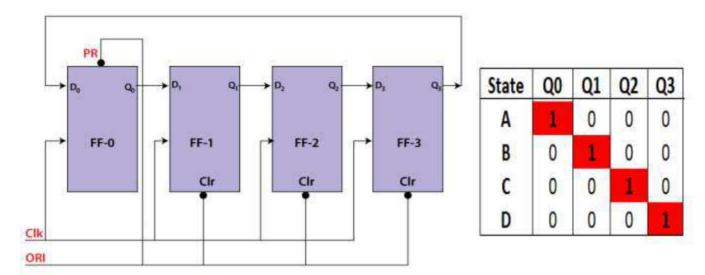

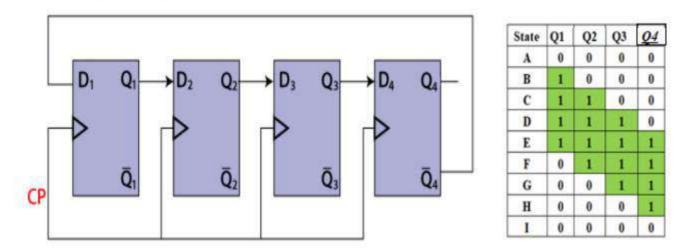

**Digital Logic Circuits-II**: Sequential Circuits, Flip-Flop Conversions, Binary counters, Ripple counters

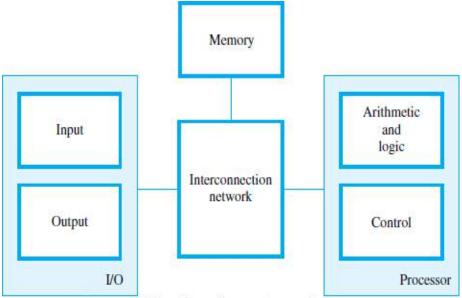

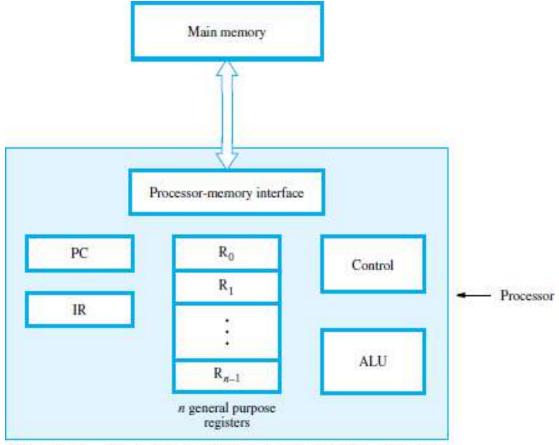

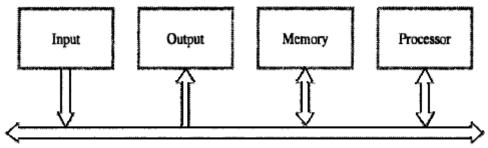

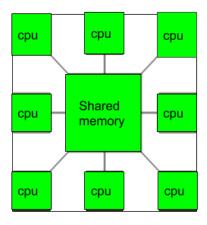

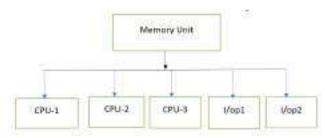

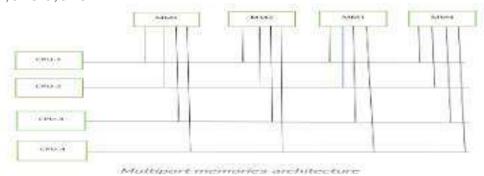

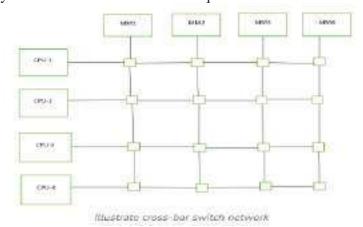

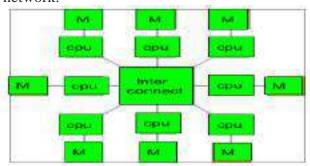

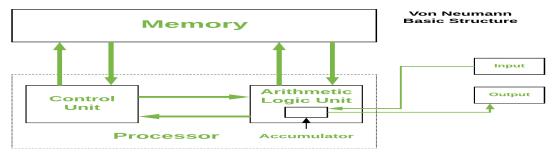

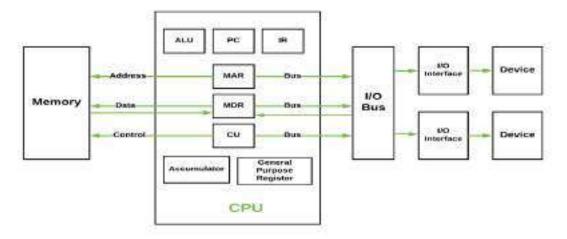

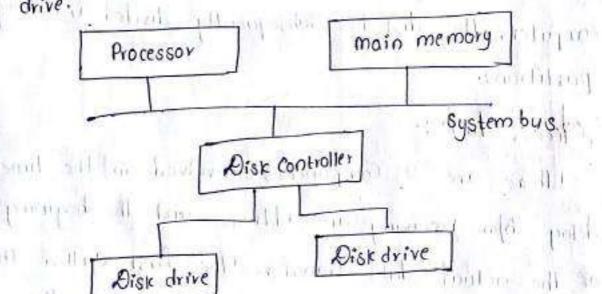

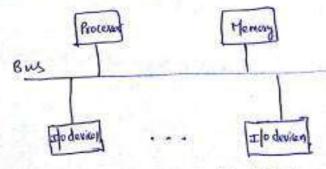

**Basic Structure of Computers:** Computer Types, Functional units, Basic operational concepts, Bus structures, Software, Performance, multiprocessors and multi computers, Computer Generations, Von- Neumann Architecture

#### **UNIT-III:**

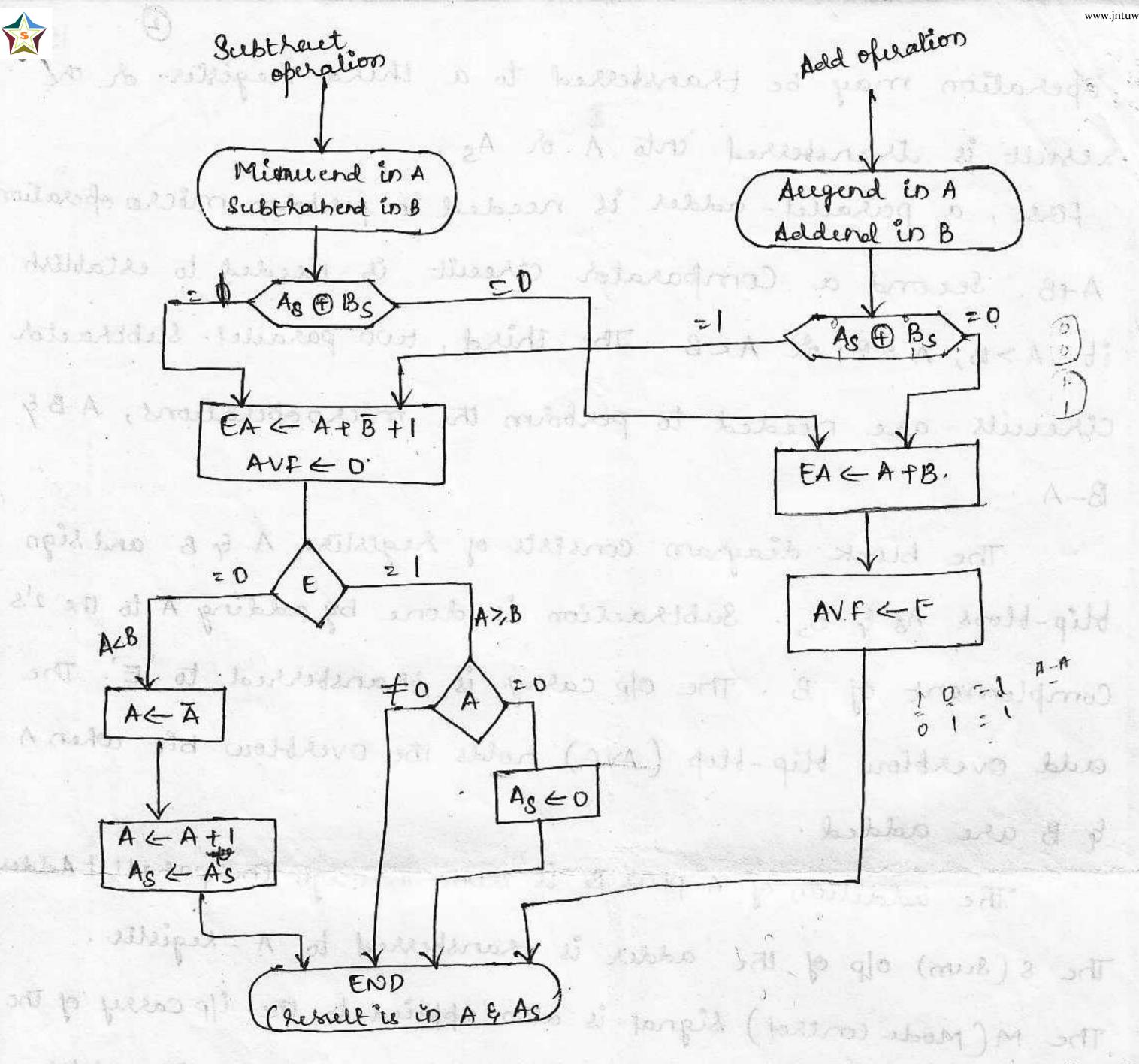

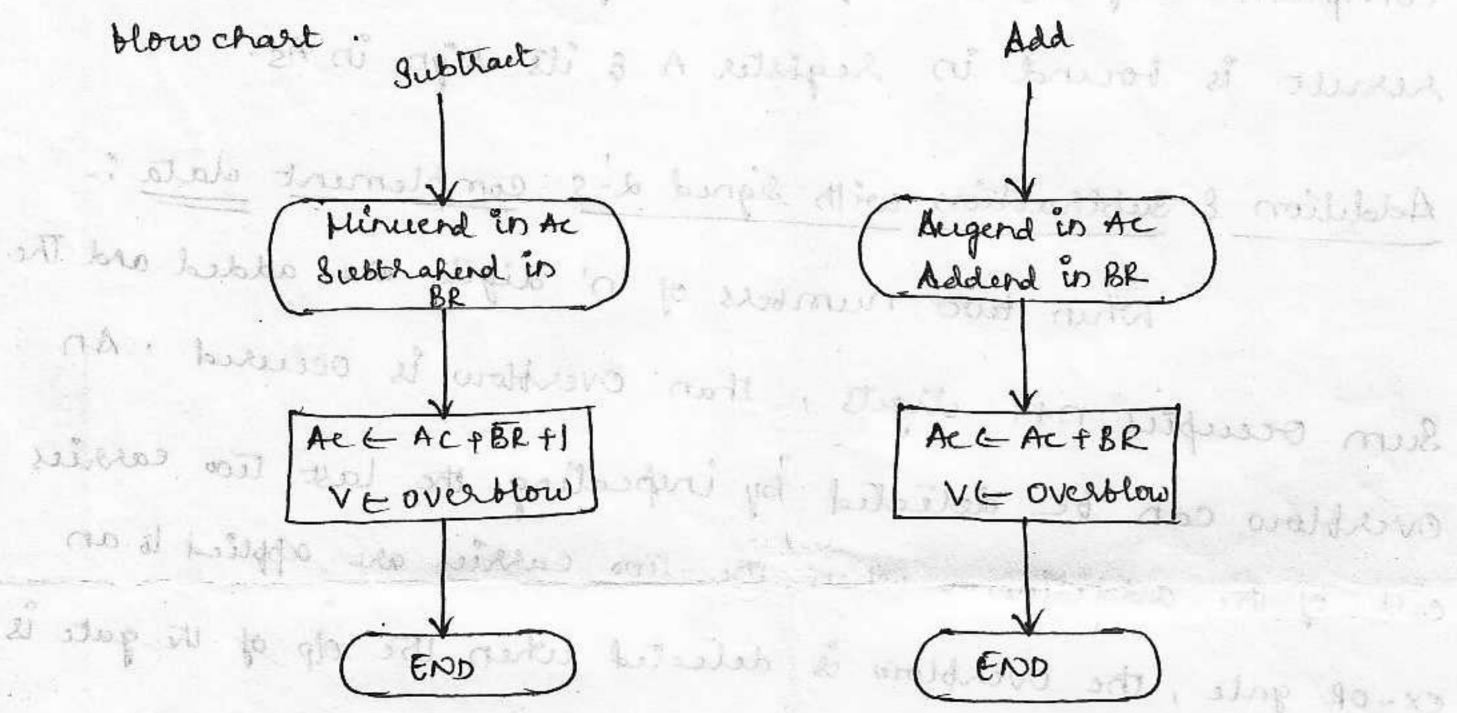

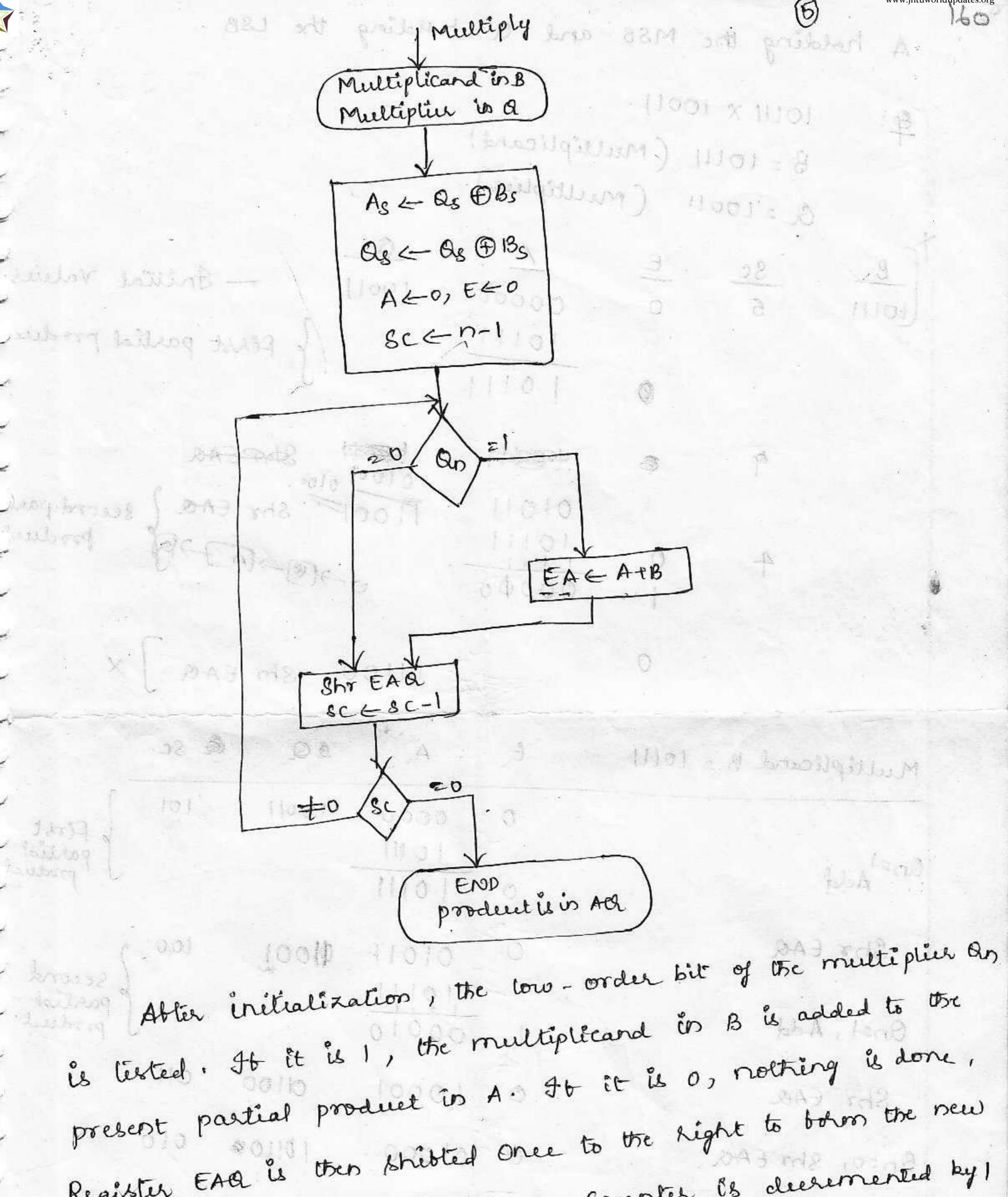

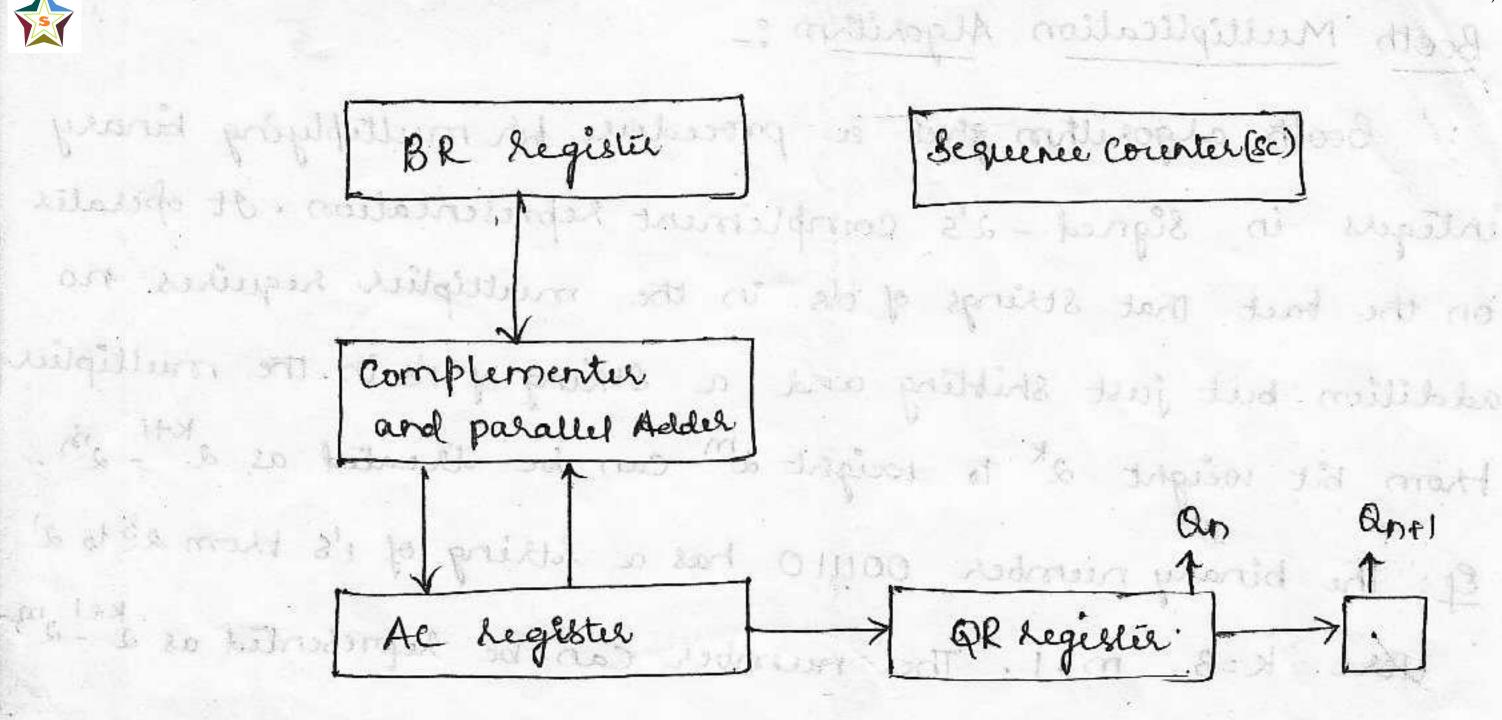

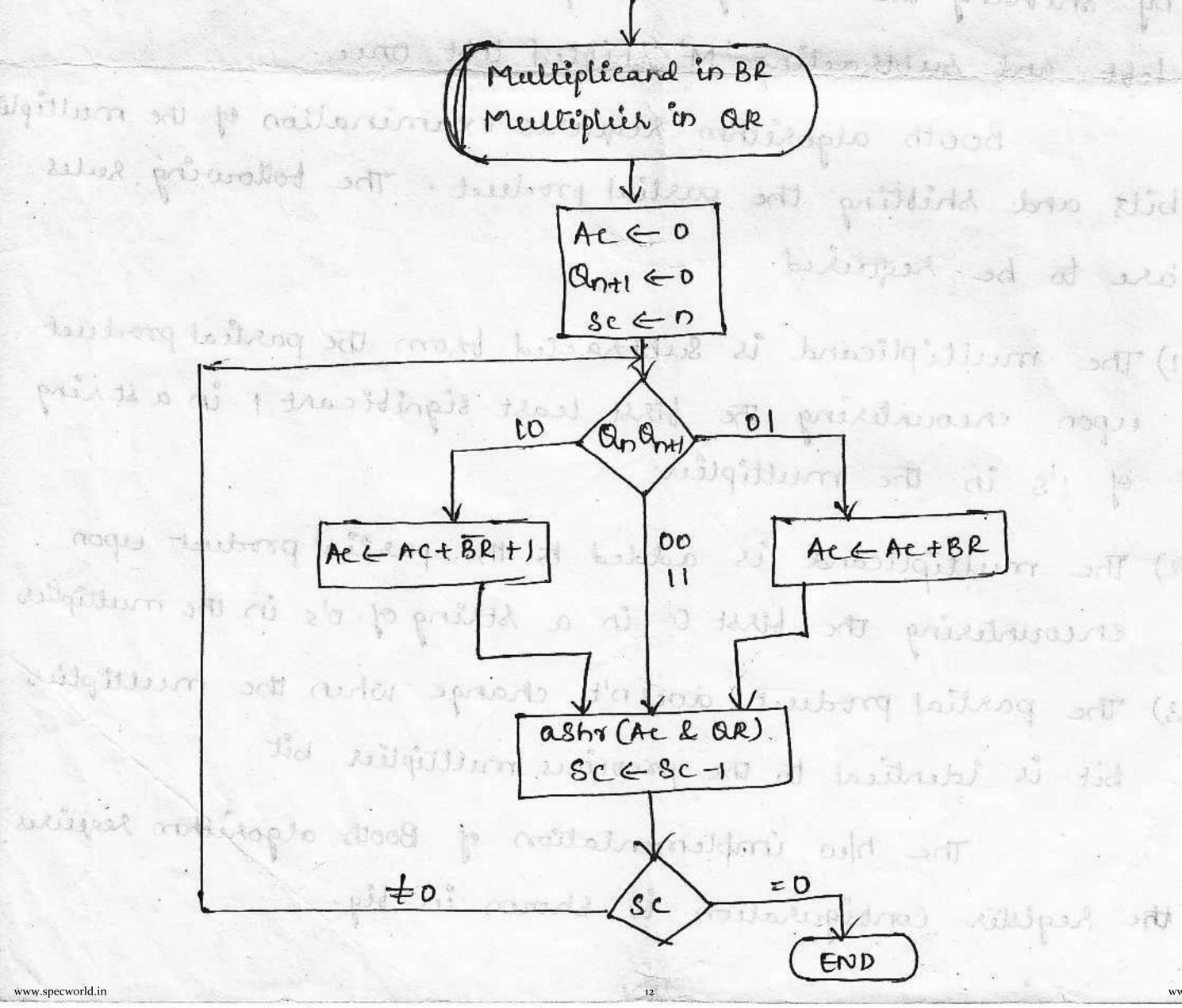

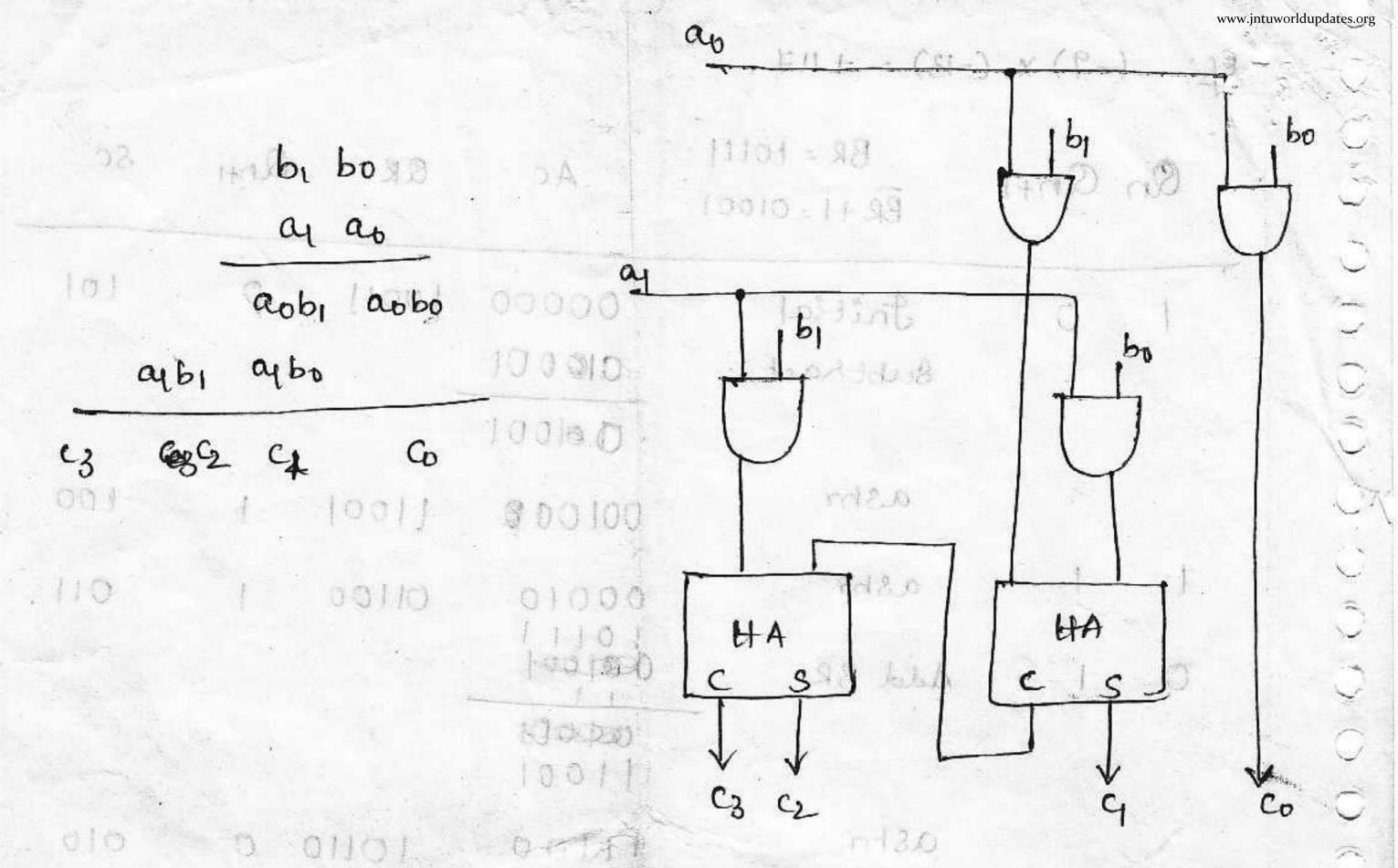

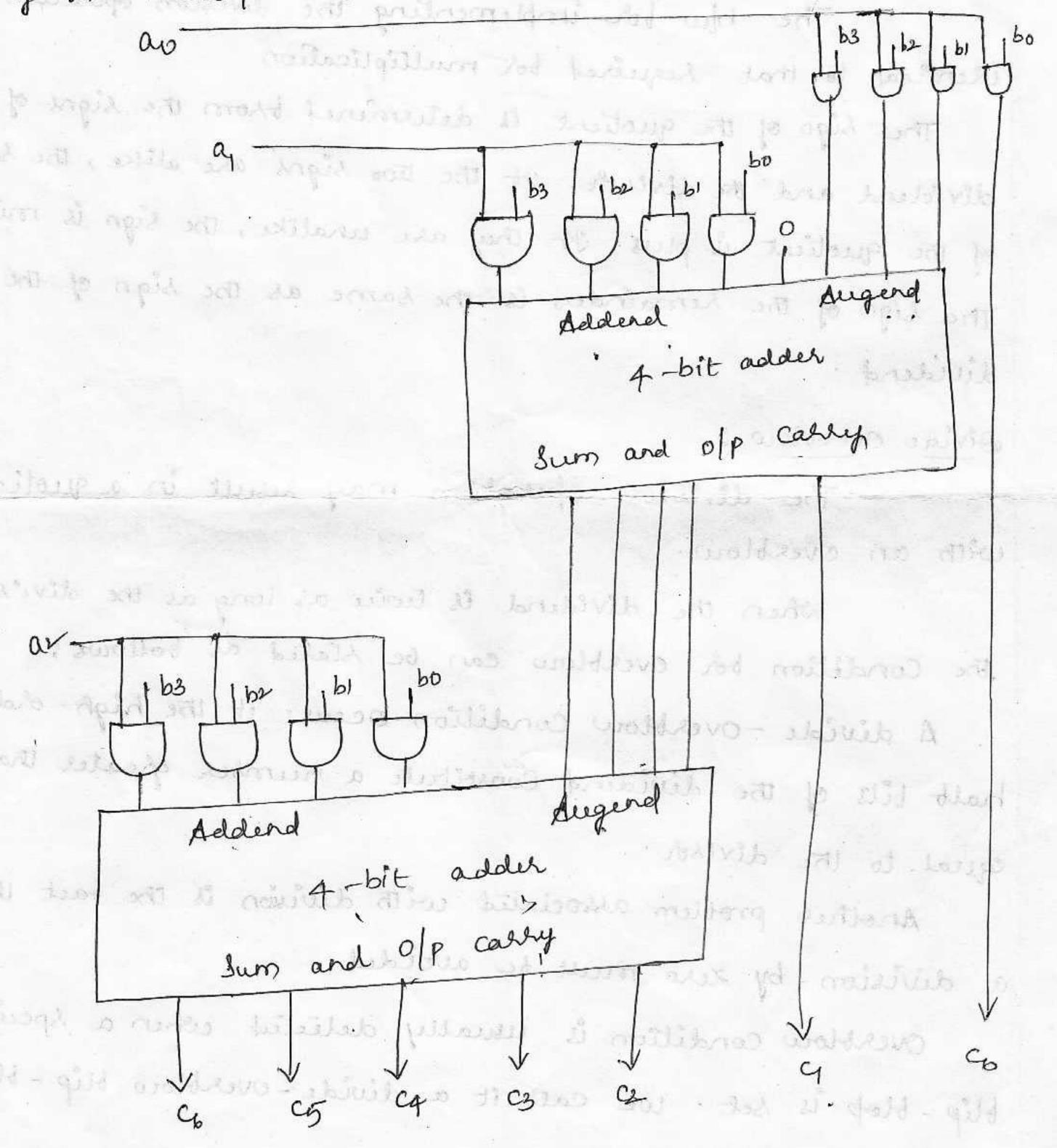

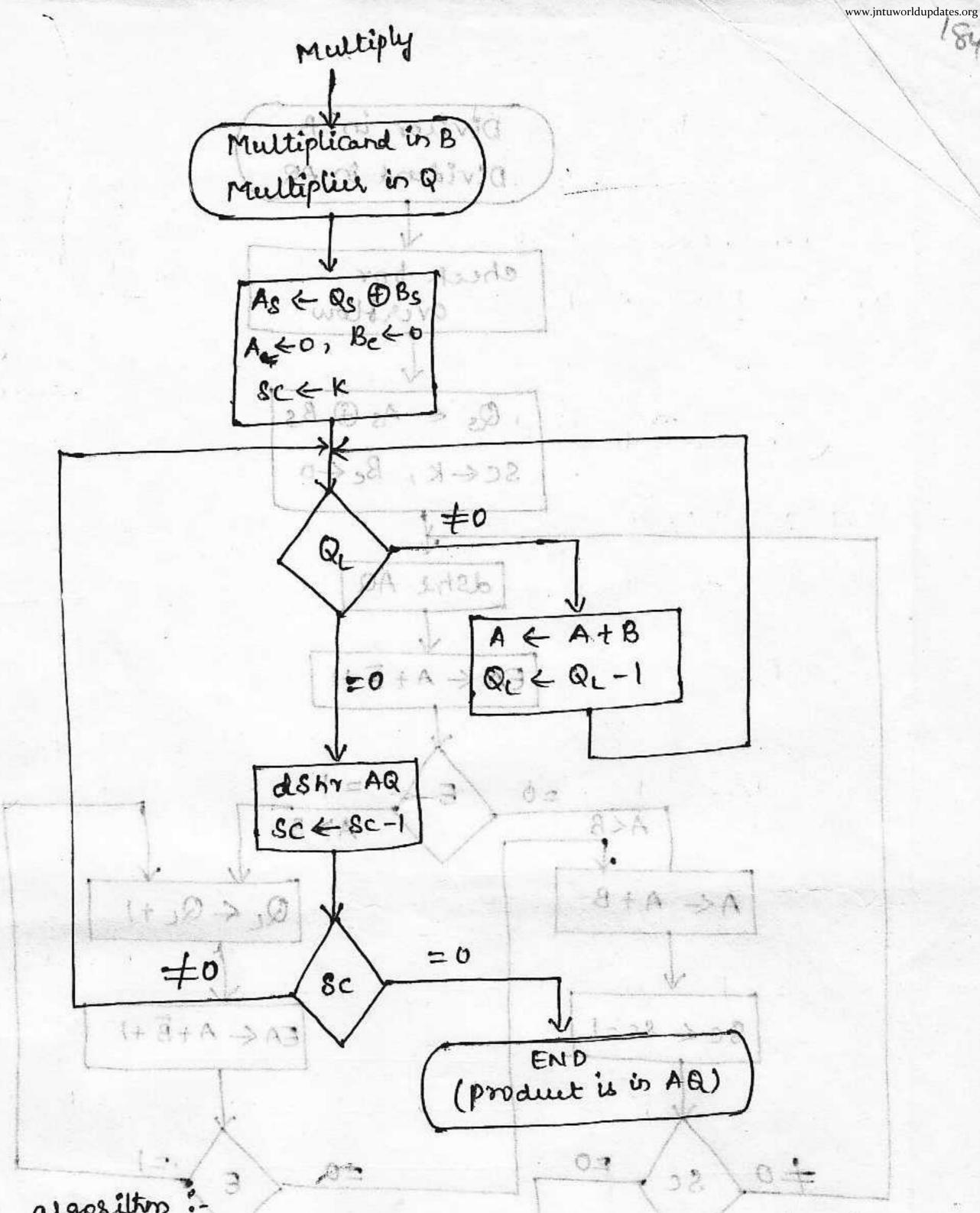

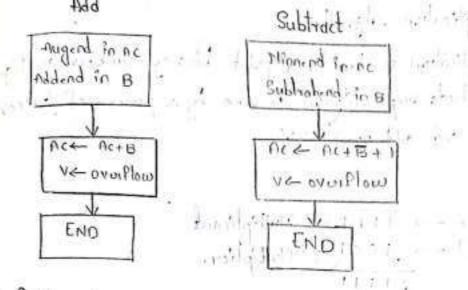

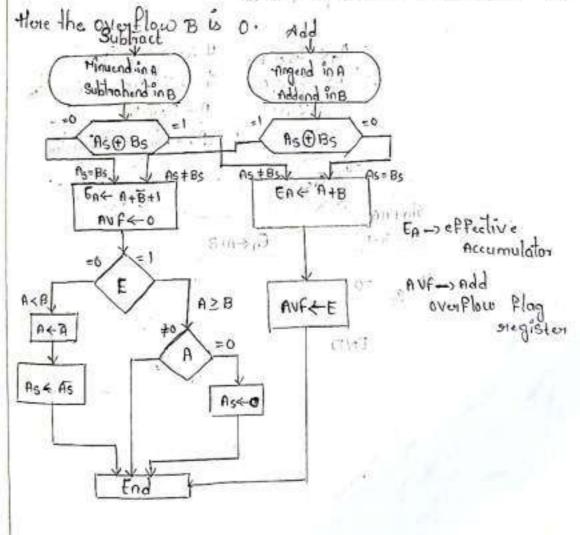

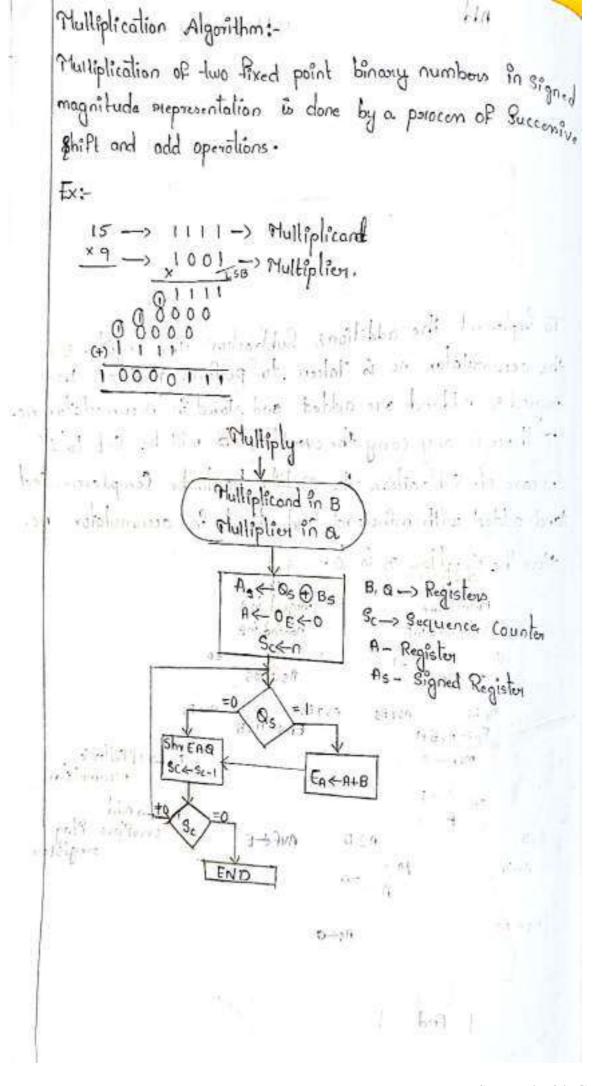

**Computer Arithmetic**: Addition and Subtraction, Multiplication Algorithms, Design of Fast Adders, Multiplication of Positive Numbers, Signed-operand Multiplication, Fast Multiplication, Integer Division, Floating-Point Numbers and Operations

**Processor Organization:** Fundamental Concepts, Execution of a Complete Instruction, Multiple-Bus Organization, Hardwired Control and Multi programmed Control

#### **UNIT-IV:**

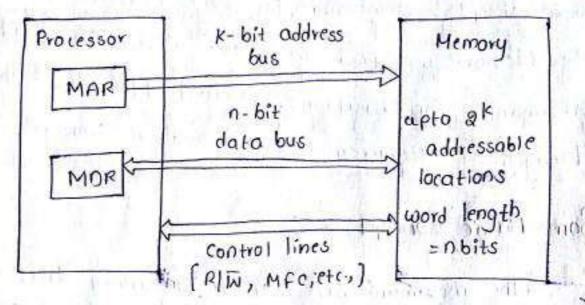

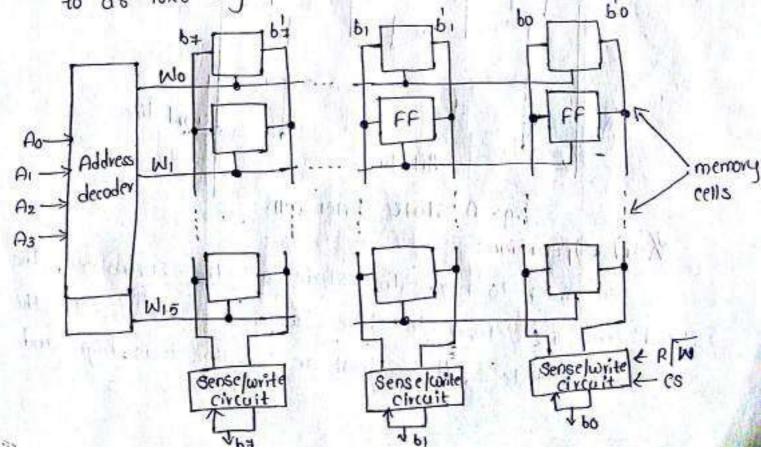

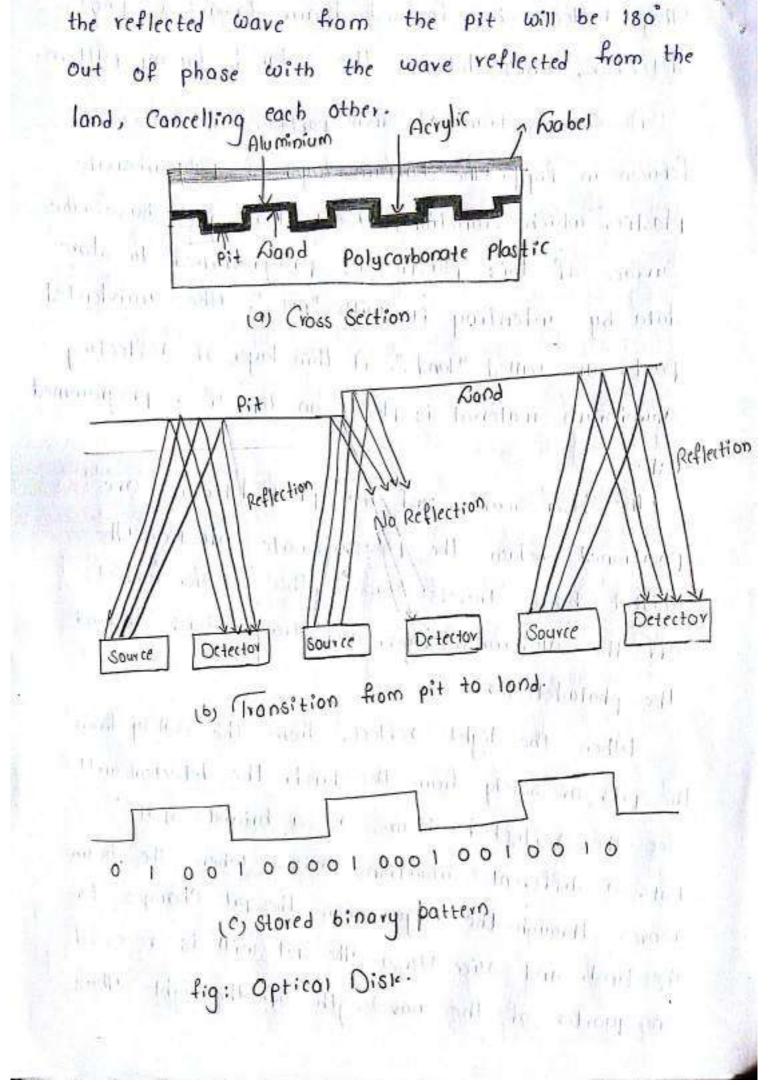

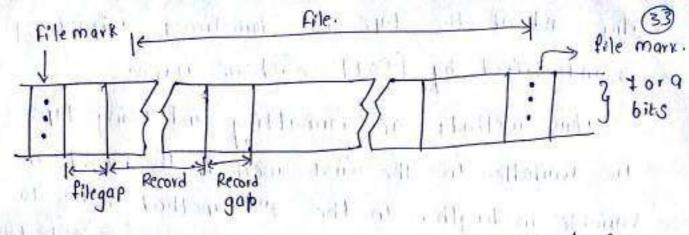

**The Memory Organization:** Basic Concepts, Semiconductor RAM Memories, Read-Only Memories, Speed, Size and Cost, Cache Memories, Performance Considerations, Virtual Memories, Memory Management Requirements, Secondary Storage

#### **UNIT-V:**

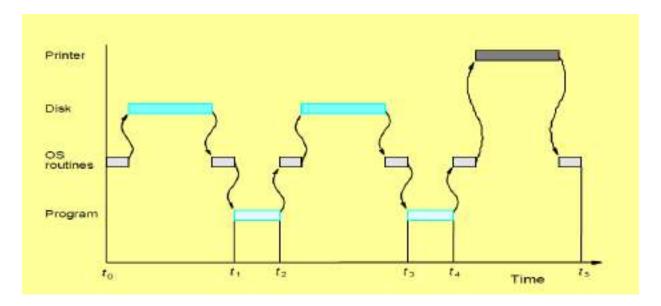

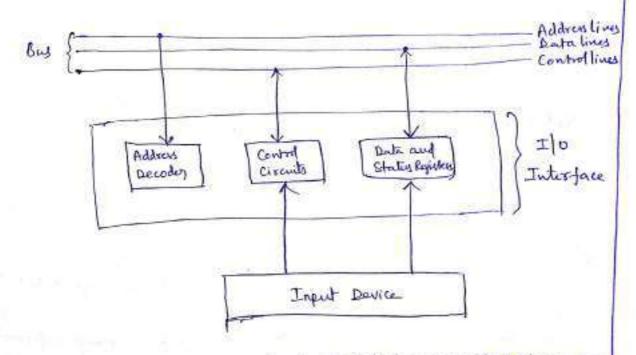

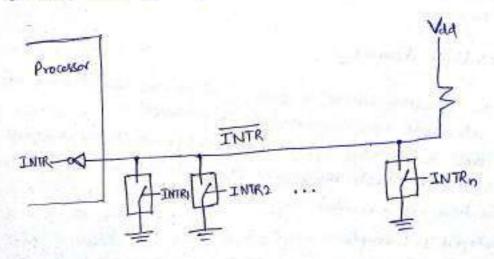

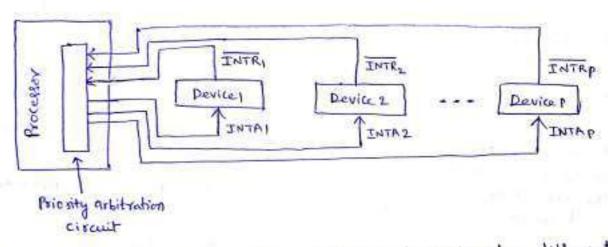

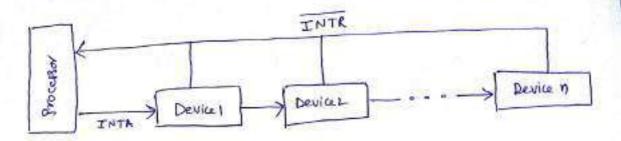

**Input /Output Organization:** Accessing I/O Devices, Interrupts, Processor Examples, Direct Memory Access, Buses, Interface Circuits, Standard I/O Interfaces

#### **Textbooks:**

- 1. Computer Organization, Carl Hamacher, Zvonko Vranesic, Safwat Zaky, 6<sup>th</sup> edition, McGraw Hill, 2023.

- 2. DigitalDesign,6<sup>th</sup>Edition,M.Morris Mano,PearsonEducation,2018.

- 3. ComputerOrganizationandArchitecture,WilliamStallings,11<sup>th</sup>Edition,Pearson, 2022.

#### **Reference Books:**

- 1. Computer Systems Architecture, M.Moris Mano, 3<sup>rd</sup> Edition, Pearson, 2017.

- 2. Computer Organization and Design, David A. Paterson, John L. Hennessy, Elsevier, 2004.

- 3. FundamentalsofLogicDesign,Roth,5<sup>th</sup>Edition,Thomson,2003.

#### **OnlineLearningResources:**

https://nptel.ac.in/courses/106/103/106103068/

#### UNT7 - 1

## DATA REPRESENTATION

Digital Systems: Digital Systems are systems that process and represent information in digital form, using discrete Values such as Os and Is to represent data, rather than continuous signal, like analog systems. Examples of Digital Systems include:

Computers (H/W & S/W), Mobile devices, Digital circuits, Microcontrollers, Digital Comeras, Digital signal præssors, personal, handheld, touch-screen devices etc.

Advantages: High Accuracy, Fast processing and transmission of data, Easy storage and retrieval of data, low noise, High reliability, Flexibility, Ability to perform complex -tasks and Calculations.

Limitations: Digital noise and evors, Depends on software and hardware reliability, cyber security risks etc.

Digital Circuits: Digital Circuits are electronic circulti that process and control digital signal, -that have only two distinct values, represented by Os and 1s. These carcuits are the building block of digital systems and one used in a wide mange a applications.

- They are Computers and Laptops, Smartphones and -tablets, Digital watches and clocks, Calculators and Alus, Digital logic gates and Flip-flops, Counters and timers etc.

- \* Digital circuits are designed using various logic pates and circuits, such as: AND, OR, and NOT gates, NAND, NOR and XOR gates, Flip-flops Multiplexers and domultiplexery etc.

- \* By using various techniques and tooks such as Boolean Algebra, Logic gates and circuits, Truth tables, K-maps, digital circuits are designed.

- > Data Representation in digital systems can be categorized into several-type as Numeric, character, smage, Audio, video, Text.

Numeric representation refers to the way numbers one represented in digital systems.

Common Representations are Binary, Decimal, Heradecimal octal, Fixed-point, Floating-point, signed, unsigned.

Binary Numbers: Binary numbers are a way of representing Information using only two digits: 0 & 1.

Binary numbers are made up of bits (as & 1s)

Each bit can have one of two values: 0 of 1

Binary numbers can be used to represent Integers, Fractions, Characters, Instructions.

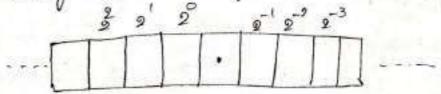

## Radix (a) Base;

It specifies the number of symbols used for a particular number systems.

#### Radix point:

In any number system, the radix point specifies the dividing line between the Integer point and fractional point.

The base (31) radix of binary numbers is 2. The binary number system is also Called ay radix-2 number system 31 base-2 number system. The binary point in a binary number separate the Integr part and fractional part

In Binary number system, the weights one expressed in terms of the powers of 2.

By adding each digit multiplied by its respective weight in the given binary number, we can obtain the decimal equivalent number.

Ex: Consider a decimal number 7,392 which represents a quantity equal to 7 thansands, plus 3 hundreds, plus 9 tens, plus 2 units

7,392 can be written as

7×103+3×102+9×101+2×10°

The decimal number system is said to be of base or radix 10, because it uses 10 digits

In a decimal number, the left most digit which has the highest weight is called as Most significant Digit (MSD) and the right most digit that has the lewest weight is called as Least significant Digit (LSD).

En: The birdony equivalent of 7,392 is Consider a binary number  $2\frac{11392}{21696}$  is 26.75  $2\frac{848}{949}$   $1\times2^{4}+1\times2^{3}+0\times2^{2}+1\times2^{4}+1\times2^{2}$   $2\frac{194}{212}$   $2\times2^{6}+1\times2^{7}+1\times2^{7}$   $2\frac{196}{53}$   $2\frac{196}{53}$

In general, a number expressed in a base-r system has co-efficients multiplied by powers of r'.

an rn+an, rn-1+ --- ag r3+a, r+ ag+

a, r++ a, r-9+ -- +am r-m.

The co-efficients as range from 0 to r-1.

Ex. of a base-5 number is

$(4021.2)_5 = 4x5^3 + 0x5^2 + 2x5^1 + 1x5^0 + 2x5^{-1}$ =  $(511.4)_{10}$

The co-efficient values for base-5 can be only 0,1,2,3 & 4.

The octal number system is a base-8 system that have 8 digits 1, 0,1,2,3,4,5,6,7.

61: (127.4) = 1×82+2×8+7×8°+4×8-1

Note that the disity 8 & 9 cannot approp

when the base of the number is greater than 10, the lettery of the alphabet are used to supplement the 10 decimal digits.

Cattery A,B, C,D, E&F are used for the

The digity of 10, 11, 12, 13, 14 & 15 respectively.

(B65F)6 = 11×163+6×162+5×16+15×160

= (46,687)10.

The Conversion from binary to decimal can be obtained by adding only the numbers with powers of two corresponding to the bity that are equal to 1.

$G: (110101)_{2} = 32$   $= 1 \times 2^{5} + 1 \times 2^{4} + 0 \times 2^{3} + 1 \times 2^{2} + 0 \times 2^{1} + 1 \times 2^{6}$  = 32 + 16 + 4 + 1  $= (53)_{10}$

## Fixed-point Representation:

Real numbers can be represented in Computer in two ways.

1. Fixed point nepresent. 2. Floating point nepresent.

1) Fixed-point

In this representation, the decimal Point is placed in a direct place.

-A number ending with a decimal point is called a whole number/Integer and a number standing

with a decimal point is called a fraction.

Ex: 45.00 - Whole number/Enteger

0.45 - Fraction number

0.1011 - Fraction number

23.25 - 23 is the whole number/Integer

25 is the fraction number

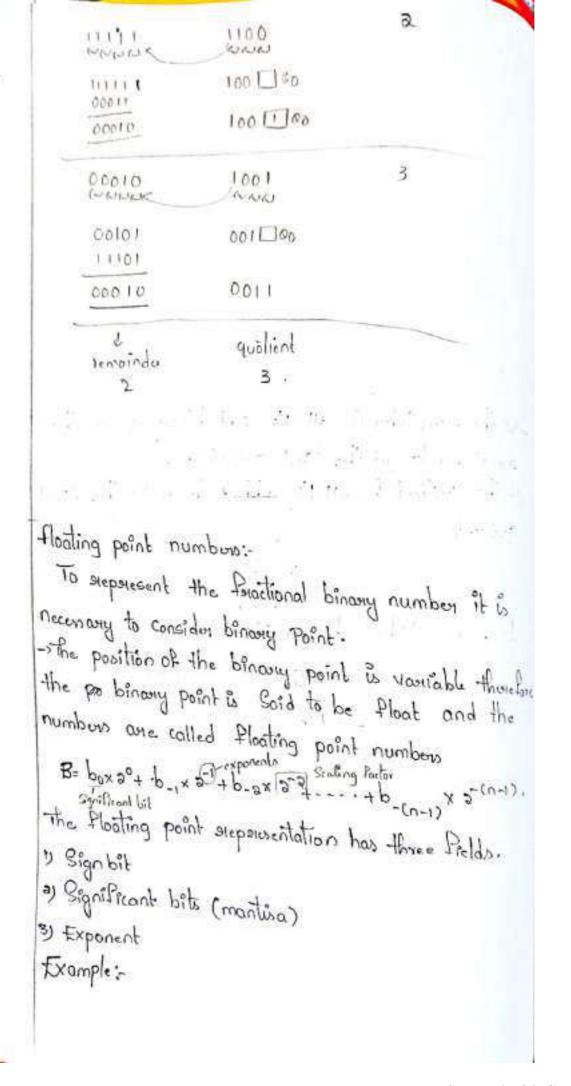

## @ Floanting point Representation

In this representation, the position of the decimal point is not specified. By this, a number can be expressed in different ways.

ex: ) (435)10, this number can be expressed as 435×10° 81 435×10' 81 4.35×10° etc.

when the radix point/binary point is Shifted to left by a 1 bit position, the exponent will be increased by 1'.

When the radix point/binary point is shifted to right by a 1 bit position, the exponent will be decreased by 1'.

(537.25)<sub>10</sub> > Mxx<sup>e</sup> M- Mantissa, e-> exponent 0.53725×10<sup>3</sup> · Y- Yadix

## Number Base Conversions:

The conversion of a decimal number in base lot to a number in base of is done by dividing the number and all successive quotients by r and accumulating the remainders.

## Ex: convert Octimal 41 to binary.

# 2) Convert Decimal 153 to octal.

Here Decimal 153 is of base 10'

Required base 85 '81, Hence 153 is divided

by 18' successively

## 3) Convert (0.6875), to binary

Conveyion of given downal of action to binary is done by a method of multiplication to get a new fraction until the fraction becomes '0' 31 the number of disits are sufficient.

0.6875

$$\times 2 = 1.3750 \Rightarrow 1$$

0.3750  $\times 2 = 0.37500 \Rightarrow 0$

0.3750  $\times 2 = 0.75000 \Rightarrow 0$

0.7500  $\times 2 = 0.50000 \Rightarrow 0$

0.5000  $\times 2 = 0.5000000 \Rightarrow 0$

## 4) Convert (0.513) to octal.

$$(0.513)_{10} \rightarrow \text{Required Radix'8'}$$

$0.513 \times 8 = 4.104 \Rightarrow 4$

$0.104 \times 8 = 0.832 \Rightarrow 0$

$0.832 \times 8 = 6.656 \Rightarrow 6$

$0.656 \times 8 = 5.248 \Rightarrow 5$

$\therefore \text{Here } 4 \text{ dists are sufficient,}$

$(0.513)_{10} = (0.4065)_{0}$

practise problem.

1) Convert (117.23) to Octal.

-AM. (65 - 1656)

# Octal and HoxaRecimal Numbers

The convention from and to binary, octal, and hexadecimal number plays an important role in digital computers because shorter patterns of hex characters are easier to necognize than long patterns of 1's & ds.

Since 23 = 8 & 24 = 16, each octal disit corresponds

to 3 binary disits and each hexaderimal disit

Corresponds to face benavy disits.

The first 16 numbers in decimal, binary octal & heradecimal number systems are listed in table.

| Decimal<br>base-10 | Binary<br>bases | octal<br>base 8 | Hexadecimal<br>base 16 |

|--------------------|-----------------|-----------------|------------------------|

| 00                 | 0000            | 00              | 0                      |

| 01                 | 0001            | 01              | 1                      |

| 02                 | 0010            | 02              | 2                      |

| 03                 | 0011            | 03              | 3                      |

| 04                 | 0010            | 04              | 4                      |

| 05                 | 0001            | 05              | 5<br>6                 |

| 06                 | 0110            | 06              | 6                      |

| 07                 | 0111            | ٥٦              | 8                      |

| 08                 | 1000            | 10              | 8                      |

| 09                 | 1001            |                 | 7                      |

| 10                 | 1010            | 12              | Λ                      |

| 11                 | 1011            | 13              | В                      |

| 12                 | 1100            | 14              | C                      |

| 13                 | 1101            | 15              | 9                      |

| 14                 | 1110            | 16              | 1911 €                 |

| 15                 | 1111            | 17              | F                      |

(1) Conversion from Briany to octal number

This Conversion is done by poutstioning the binary number into groups of three disits each, starting from the binary point and proceeding to the left and to the right.

The corresponding octal disit is then assigned to

each group.

Ex: convert binary (10110001101011. 111 100 000 110) anto extal number.

10110 001 101 011 . 111 100 000 110 5 3 7 4 0 6 => (26153.7406) g.

(ii) Convension from Binary to Hexadecimal number

This conversion is done by partitioning -the binary number into groups of four disits each,

Starting from the binary point and proceeding to

the left and to the quight.

The corresponding hexadecimal digit is then assigned to each group.

-Hexadecimal number

iii) Conversion From Octal 81 -Hexadecimal to

In case of octal number, each octal disit is convented to its three digit binary aquivalent. similarly, each thexadecimal dist is convented to its four thigit binary equivalent.

673.124

=> (110111011.001010100)2

2) -Hexa to bindary

(306.0)16 => (?)

3 0 6 ° D

0011 0000 0110 1101

> (0011 0000 0110.1101),

Practise problems:

1) Find the binary representation of (135) 10

-Ans: (135) (1000 011)

2) Find the octal nepsesantation of (135)10 -Ans: (135)10 - (207)8

3) Convert the following numbers with the indicated bases to decimal.

a) (102)4 b) (5134)6 c) (9762)14 d) (206)9

4) Convert the hexadecimal number DB4F to binary, and then convert it from binary to octal.

5) Explose the following numbers in decimal.

a) (10001.101)2 b) (52.5)16

c) (342.54)8 d) (101010.101),

really fall remaindered to the persons of the professional

Address of the state of the sta

the state of the s

the state of the s

many of the second seco

The state of the s

#### COMPLEMENTS

Complements are used in digital computers.

To simplify the subtraction operation and for logical manipulation.

There are two types of complements for each base-r system. The Radix Complement and the diminished Radix Complement. The first is referred to by the r's complement and the Second by the (r-1)'s complement.

when the value of base it is substituted in the name,

the two-types are neferred to as the 2's complement

and 1's Complement to binary numbers and the

10's Complement and 9's complement to decimal numbers.

## Diminished Radia Complement

Given a number N in base r having 'n' digit, the (r-1)'s complement of N, that is it diminished radix complement is defined as (rn-1)-N.

Tor decimal numbers, r=10 & r-1=9, so the 9's complement of N is (10n-1)-N. Here 10n represents a number that consists of a single 1 followed by 'n' o's. 10n-1 is a number nepresented by 'n' o's.

Ex: If n=4, we have 10n = 10,000 & 10n-1=9999

The 9's complement of a decimal number is obtained by Subtractly each digit from 9.

(x; 1) The 9's Complement of 546700 is

999999

- 546700

453299

11) The 9's Complement of 012398 is

99999

-012398

987601

For binary numbers, r= 2 & r-1=1. so the is complement of N is (2n-1)-N. Here 2n is represented by a binary number that consists of a 1 followed by 'n' o's. 2<sup>n</sup>-1 is a benony number superesented by 'n' 1's. Ex: y n=4, we have 24 = (10000) & 24-1= (1111), Thus, the is complement of a binary number is obtained by subtracting each digit from 1. Therefore, -the is complement of a bincony number is formed by changing 1s to o's & d's to 1's. Ed: i) The i's complement of 1011000 is 010011 ii) The i's complement of 0101101 is 1010010. The (r-1)'s complement of octal of hexaderimal number is obtained by subtracting each dist

from 7 81 & (decimal 15) nespectively.

practise problems:

Find (a) The diminished radix (g's) complement of (135).

(b) Find is complement of the binoary numbers

i) 11001101 ii) 10100101 iii) 01001001

Radix Complement

The x's complement of an n-digit number N in base x is defined as  $x^n-N$  for  $N\neq 0$  and as 0 for N=0.

The is complement is obtained by adding 1 to the G-1)'s complement, sine M-N = (Cr^1)-N)+1.

Ex: The 10's complement of decimal 2389 is?

10's complement is obtained by adding 1 to the

9's complement value.

. . q's complement of 2389 is

-Adding 1 => + 1 7610

10's complement of (2389) is (7611).

( ii) The 2's complement of binary (101100), is ? 2's complement is obtained by adding 1 to the 1's complement value.

1's complement of benoony 1011,00 is. -Adding 1 => + 010100

Note: The complement of the complement restores the number to its original value.

practise problems:

1) Find the radix (10's) complement of (135)10

11) Find the 2's complement of binary numbers

a) 01101000 b) 10110100 c) 10100101

(ii) Find the 10's complement of decimal numbers

a) 87,000,367 b) 99,999,000

c) 56, 783,223

iv) Find the 8's complement of (1740) &

v) convert (1740), to binary.

# Subtraction with &s Complement (Subtraction with &s Complement) Minuend - Subtraction (M-s)

- 1) Equate the number of digits by padding appropriate number of zerous infront of the numbers.

- 2) Find the 1's complement to subtrahend and add with Minuerd

- 3) sift carry is generated, the result is positive and the carry is discorded to get the final negult

- 4) If cours is not openerated, the negult is negative, and the resold take 8's. Complement of the result to get the final negult.

Ex: Using 10's complement, subtract 72532-32

-Here M= 72532 { S= 3250

1) To equate, add o' at infront of 's' i.e., 03250

2) 10's Complement of 's' is obtained by

W.K.t. 10's Complement = 9's Complement +1

9's Complement of s'= 99999

-03250

-Add 1 => -11

-Add 1 => = 11 10's compledy'=> 96750 NOW -Add with 'M' 96750 + 72532 Coon 69282 3) Here, the Coop is generated, the regult is positive, Carry is discarded .. Final Result is 69282 which is positive.

practise problems

of Given the two binary numbers X = 1010100 } Y= 1000011, Pentim the subtraction

a) X-Y & b) Y-x by using 2's complements.

Suttraction with (5-1)'s Complement: Note: To do the subtraction using (r-1)'s Complement, If the carry is generated, Add that carry to the least significant digit position of the result to get the final Yesutt.

Ex: Given binary numbers X= 1010100' & Y=1000011 perform the subtraction using 1's complement. a) x-y X- y = 1010100 - 1000011

X = 1010100 1) 1's complement of Y = 0111100 -Add with X and 0010000

X-Y= 0010001.

b) Y-X = 1000011-1010100 1's comple. of X=0101011

-Add with = 1000011

of negat to get final negat.

- (1101110) => 11 - 0010001

## Practise problems:

- 1) Perform the subtraction using 2's complement a) 10011-10001 b) 1001-101000

- a) 7523-4567 b) 230-1204

## 1 Signed Binary numbers

positive Integers (including zero) an be represented as unsigned numbers.

To represent negative integers, a minus segn is placed in the left most position.

In case of binary numbers, the sign bit is indicated as 'o' for positive is '1' for negative.

If the binary number is signed, then the leftmost bit represent the sign & the rest of the bits represent the number.

If the binary number is assumed to be unsigned, then the left most bit is the most significant but of the number.

Ex: For decimal '9', the bindery is 01001.

- Here '9' is unsigned bindery or

+9 is signed bindery because left most

bit is 'o'

The string of bits 11001 nepresent the binary equivalent of 25 considered as an unsigned number of binary equivalent of -9 when considered as a Signed number. Because the 1' in the leftmost position designates a negative of the other four bits represents binary 9.

The signed binary numbers are represented in a format Called signed Magnitude form.

In a signed binary number, the left most bet (i.e., MSB) represents the sign of the number and all the remaining bits represent the magnitude of the number.

Some of the 8-bit signed binary numbers are

+6 = 0000 0110

-14 = 1000 1110

+28 = 0001 1100

-64 = 1100 0000

In unregned birmay number, all the bits represent the magnitude.

- > If the signed binary number is negative, it can be represented in three ways

- 1) Signed-magnitude form

- 11) signed I's Complement form

- iii) signed 2's Complement fam

- > If the Signed binary number is possible, then the signed magnitude from, signed is complement from all are identical.

Representation of signed binary numbers using 2's complement and 1's complement:

- 1) If the signed binary number is positive, the sign bit 'o' is placed for such numbers, i's complement and 2's complement are equal to signed magnitude form.

The signed binary number is negative, then the magnitude is represented in is complement (3) 2's complement from, & then the sign bit 1' is placed infrom of MSB.

Ex: Represent '-5' three ways with 8 bits:

- a) sigmed magnitude

- b) Signed 1's Complement

- c) signed 2's Complement.

Sol: Given number is -5'

- a) Signed-magnitude with 8 bits

1000 0101

Signal

- b) signed is complement

- c) signed 2's complement 1's complement +1

⇒ (1111 1011)<sub>2</sub>

Practise problem

Represent +51 & -51 In signed magnitude from, is complement & 2's complement Formats.

Table: Signal Binary numbers.

| Docimal | Signed - 2's<br>Complement | Stymed-1's Complement | Signed Mozgratude |

|---------|----------------------------|-----------------------|-------------------|

| +7      | 0111                       | 0111                  | 0111              |

| +6      | 0110                       | 0110                  | 0110              |

| +5      | 0101                       | 0101                  | 0101              |

| +4      | 0100                       | 0100                  | 0100              |

| +3      | 0011                       | 0011                  | 0011              |

| +2      | 0010                       | 0010                  | 0010              |

| +1      | 0001                       | 0001                  | 0001              |

| +0      | 0000                       | 0000                  | 0000              |

| -0      | -                          | HITT                  | 1 1000            |

| -1      | 1111                       | 11.10                 | 1001              |

| -2      | 1110                       | 1101                  | 1010              |

| -3      | 1101                       | : 11 00               | 1011              |

| -4      | 11 00                      | 1011                  | 1100              |

| -5      | 1011                       | 1010                  | 110.1             |

| -6      | 1010                       | 1001                  | 1110              |

| -7      | 1001                       | 1000                  | 1111              |

| -8      | 1000                       | -                     | Se Se             |

|         |                            | 100/100 1 70          | 8 85 <sup></sup>  |

## Digital Logic circuity-I

Digital logic circuits are electronic circuits

that process information in the firm of binary data (os & 15)

These are the building blocks of digital systems & one designed to perform specific tasks, such as Arithmetic, logical operations, Data storage and retrieval, control & Sequencing.

The Components of digital logic circuits one Logic gates (eg. AND, OR, NOT), Flip-flops (eg. SR, D, JK, T) Counters, Registers.

B A particular digital system may define logical as a signal equal to over logic 1 as a signal equal to 5v.

Logic Grates: Logic gates are electronic Circuits that operate on one of more physical input signals to produce an output signal.

The Godes are blocks of handware that produce the captivalent of logic-18) logic-0 output signals if input logic nequirements are satisfied.

There are three basic Logic gates: AND, OR and NOT Gates

The graphic symbols used to designate three types of gates are shown in Fig.

A D Z=A+B A Do Z=A

Two input-AND Two input OR NOT Create 8)

Grate Grate Grater

AND Gate Thes logic gate performs the product of two of mole inputs. This operation is represented by a dot or by the absence of an operator.

For eq., A.B = Z & AB = Z is read "A ANDB is equal to z".

Gt means that output z=1 if and only if A=1  $\in$  B=1. Otherwise output z=0.

The result of the operation of basic logic function of AND Grate is A.B = Z.

of two 31 more inputs. This operation is represented by a plus (+) sign.

For eq., A+B=z is nead as "A OR B is equal to z" which means output z=1, if A=1 of B=1 or B=1 or A=1 or A=1 or B=1 or A=1 or A=

If both A=0 & B=0, then Z=0.

Not combe This logic gate performs the inversion of the given input. This operation is represented by an overbon (-)/prime (!)

for eq., A' = Z ( $\overline{A} = Z$ ) which gread as "Not B is equal to Z''

If A=1, then 2 20, but if A=0, then 2=1.

The NOT Grate is also referred as complement operation since it changes a 1-to a and a otol. Touth tables: It is a table of all possible combinations of the variables showing the relation between the inputs and outputs.

The truthtables of AND, OR & NOT age given

|   | AN | 0   |   | OR. | a 11 S |     | N | OT          |

|---|----|-----|---|-----|--------|-----|---|-------------|

| A | В  | A.B | A | 8   | A+B    |     | A | $\forall_I$ |

| 0 | 0  | 0   | 0 | 0   | 0      | (0) | 0 |             |

| 0 | 1  | 0   | 0 | 1   | 1      | 23  | 1 | 0           |

| } | 0  | 0   |   | 0   | •      |     |   |             |

| 1 | 1  | 1   | ŧ | 1   | 1      |     |   |             |

In binary anothmetic, It is 10, whereas in binary logic it is It is 111.

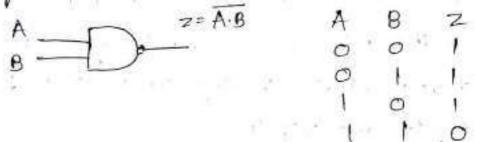

## Universal Logic Gates:

These gates one a set of logic gates that Can be combined to perform any possible logical operation.

There are two universal cogéc gates...

8. NOR Grate It is a combination of OR & NOT operations. It is the complement of OR function by a small cincle.

Small cincle.

A B Z

The Boolean function can be nepresented in a truth. -table. The number of rows in a truth table is 27, where n is the number of variable in Boolean function.

# Simplification of Boolean functions:

When a boolean expression is implemented with logic gata, each team acquains a gate & each Variable within the term designates an input to that gate. A variable within a term, either in complemented form (a) in uncomplemented from is said to be a literal.

The techniques and to simplification of Boolean expression is given below

1) Multiply all variables necessary to gremove parantheis

2) Look for adentical terms only one of those terms is Inclained & all other terms are dropped.

Ex: AB+ AB+ AB : AB

3) Look for a variable & its regation in the same term. This tum can be dropped.

EXI ABCC' - AB(0) = 0

4) Lookfor pains of terms that and identical except one Variable is appearing extra in one of the two teams. Then The larger term can be dropped.

ABC'+ ABC'O'= ABC' (HO) = ABC'

5) Look for pains of terms which have the same vocatables Such that a variable in one of the term is complemented while in the other term it is not, then such terms are combined in to a single term by dropping that vaccable. Eq: ABC O+ ABC O= AC O (B+B)

= Acio

Eg: Reduce the expression for A [B+c' (AB+Aci)] sol: Given f= A [B+c' CAB+ Ac')] = A (B+C'(AB) (Ac'))

= A [B+c1 (A1+B1) (A1+c)]

= A (B+c' (A'A'+ A'C +A'B'+ B'C))

= A[B+ A'c'+ A'cc+ A'B'c'+ Bcc']

= A[B+ A'C'(1+B') +0]

= AB+ A·AIBICI

= AB.

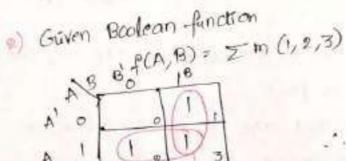

Any Boolean function can be expressed as a sum of minterms (8) as the product of maxterms. Boolean functions expressed as a sum of minterms is known as Connected sop from a minterm cononical from 8) sum of minterms form, & Boolean functions expressed as a product of maxterms is known as canonical pos from 8) maxterms Cononical from 8) maxterms cononical from 8) maxterms cononical

Standard forms: In this, each term of a Boolean function may contain one, (31) two (31) any number of literals.

There are two types of standard forms.

- 1) sum of products form (sop)

- 2) product of sum form (pos)

The sop is a firm in which a Boolean function contains AND-terms called product terms, of one of more literally each. The sum denotes the ORing of these terms.

Eq: 41+ x4+ x4 z1

Here, three product terms 4, x9 & x/yz/

of 1 literal, 2 literaly & 3 literally suspectively,

The pos is a firm in which a Boolean function

Contains or terms called sum terms, of one of mole

literally each. The product denotes the AND ing of these terms.

Eg. Fr = x (y+2) (x+4+2+4)

of 1 literal, 2 literals & 4 literals suspectively

# Conversion of sop form to canonical tom:

To convert sop form to canonical tam, steps below tollard one:

1) Find the missing literal of each product term if

2) AND each product term that has missing literal/ literals with term/terms frimed by oking the literal s its complement.

3) Expand the terms by applying distributive laws 4. notider the literal in the product terms.

u) Reduce the expression by amitting the superted product terms if any.

Eq: convert the function f(A,B,c): AB+BC+AC into

sol: Given P(A,B,C) = AB+BC+AC = AB(C+C')+(A+A')BC+AC(B+B')

= ABC + ABC + ABC + A'BC + ABC +

AB'C

f(A,B,C) = ABC + ABC + A'BC+ AB'C

P(A,B,C) = ABC + ABC + A'BC - AB'C = m7 + m6 + m3 + m5

. . Canonical sop form = Zm (3,5,6,7) - ABC + ABC + A'BC+AB'C

Canonial postam: TTM (0,1,2,4)= (A+B+c) (A+B+c') (A+B+c)

(A +B+C)

Note: The Canonical postam function form a Canonical Sop function can be written by writing the missing decimal numbers from the connanial sop fam function & vice versa.

· Canonical pos form from given pos form:

1) Find the missing literal in each sum-term if

2) OR each sum term that hay missing literal/literaly

with the team / teams formed by ANDing the Literal

3) Expand the terms by applying distribution law

& reader the literally in the sum terms.

4) Reduce the expression by omitting repeated sunderms if any.

Eq: Convert the postunction F(A,B,c) = (A+B)(B+c)(A+c) to Cononical pos form & Cononical sop form. Gaven F(A,B,C) = CA+B) (B+C)(A+C). : A+BC = (A+B)(A+C) = (A+B+CC) (AA+B+C) (A+C+BB) = (A+B+C) (A+B+C') (B+C+A) (B+C+A') (A+C+B) (A+C+B) = (A+B+c) (A+B+c) (A+B+c) (A+B+c) (A+B+c) (A+B1+c) = (A+B+C) (A+B+C')(A+B+C)(A+B+C) = Mo. M1. M4. M2 = 95M (0, 1, 2,4) Canonical pos: MM (0,1,2,4) , (A+B+c) (A+B+c) (A+B+c) (A+B+c)

Canonical Sop = Zm (3,5,6,7) = A'BC+ AB'C+ ABC'+ABC

# Digital Logic Gatis:

AND Gote: An AND Grate has two of more inputs but only one output. The output will be at logic 1 State only when each of its inputs is at logic 1 state. The output is at logic o state even if one of its inputs is at Logic o' State.

The logic symbol & touth table of a two input AND Grate is shown in figure.

## Gate Level Minimisation

We know that the Boolean functions can be mealized using logic gates. The total number of logic gates and literally can be neduced, if the boolean function is simplified. The simplification of a boolern-function, is required for neducing - the complexity and cost of designing of the logic concept. -> During the process of simplification using Boolean algebra,

one must know the Boolean laws, gulles, proporties and the Bloms -tholoughly. And also it is nequired to predict the successive. steps to get the simplest expression.

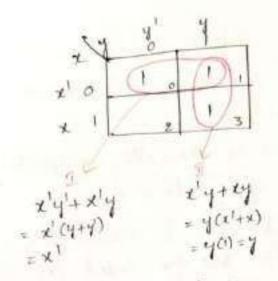

- The map method gives us the systematic procedure to simplify the gren Booloon function. It is also called ay Kannaugh map method 31 K-map method.

The map method was first proposed by vertch & matified by Karraigh, hence map method is also called

as veitch diagram 31 Karnaugh map.

The map method (a) Kannaugh-map (3) K-map method.

The K-map is a diagram made of square basis. Each square box is called as a cell that nepresents either a minterm da max term.

-- The simplified function produced using K-map is present in any one of the standard forms i.e., either in product of sum (1005) form of sum of products (sop) form.

The simplified function should have less number of -terms & each-term shalld have minimum number of literaly

-> A K-map contains on cells for the n-variable badeon

expression.

17- A 4- variable boolean expression contains 24=16 cells.

#### 2 - variable K-map:

In a 2-variable K-map, there are 2=4celly each cell nepresent a mintern (81) a max-term.

A -two variable K-map with mindern representation & madeim giepresentation one as shaon beloo

with mintern represent.

A'O A'B'O A'B IT A=0=>A' A A'B O A'B' IT A=1=>A'

A'O A'B'O A'B IT A=0=>A' A A'B O A'B' IT A=1=>A'

A'O A'B'O A'B IT A=0=>A' A' A'B O A'B' IT A=1=>A'

Fig: 2- Variable K-map with

Fig: 2- variable K-map with maxterm nepresent.

#### 3-variable K-map:

A 3- variable K-map contains 23 = 8 cells. Each Cell grepresents a minterm 31 a marcherm.

Here the manterns of maxterns one overlanged in Gray code - sequence but not in Malinary binary sequence.

The advantge of Gray code over normal bring sequence is that only one bit position is having a change between its present value to previous value 31 between its present value to its next value. The 3-vaciable K-map with mintern & martern grepresentations are

given in below figure. O NEC NEC NEC ABC ABC ABC

Fig: 3- variable K-map with minterm grepresent.

| BC  | arc    | B+c'         | B'+c'       | B+c    |

|-----|--------|--------------|-------------|--------|

| AO  | A+B+C  | A+B+c        | Atstel<br>3 | A+8+C  |

| A'I | Al+B+C | A1+8+c1<br>5 | Al+8+d      | A128+0 |

Fig: 3 variable K-map with martem supresent

4- variable K-map.

A 4- variable K-map contains 24=16 cells. Each Cell Contains either minterm 3) marterm.

A 4- variable K-map containing minterm representation & maxterm nepresentation one of shown

| bel                             | 00 | اولم ا  | do         | CD          | C01    |

|---------------------------------|----|---------|------------|-------------|--------|

| A <sup>l</sup> B <sup>l</sup> A | 00 | AlBlc'o | A'8'c      | A'8'co<br>3 | 2      |

| A <sup>1</sup> B                | 01 | A'8c'0' | A1820<br>5 | A'BCO       | A'BCO' |

| Ав                              | IJ | ABc101  | ABC'D      | A8c0<br>15  | ABCO'  |

| AB'                             | 10 | AG1c1   | AB'c'b     | MB/cD       | MB'col |

Fig: 4- variable K-map with mintern nepresentation

| 200      | 9 C+0     | C+01           | c1+01            | C+10          |

|----------|-----------|----------------|------------------|---------------|

| A+800    | 1         | A+B+c+3        | A+8+4+b          | A+B+c+o       |

|          | AHB+CHD   | A+B+C+d<br>5   | A+8+d+d          | 6 AHB4        |

| A'+B' 11 | A1+18+C+9 | A1+8+c+0<br>13 | Al+8l+cl+d<br>15 | A484449<br>14 |

| AUR 10   | AL+B+C+D  | A1+8 +C+       | Al+8+chb         | A+8+c+0       |

| 10 10    | 8         | 9              | п                | 10            |

Fig: 4-variable k-map with martern supresent The following-terms are defined with neglect to Kimps simplification.

poir. A group of two adjacent minterms 21 macterns is called as a pair. A pair climinates one variable from the mesultant term

From its negations term.

octer: A group of eight adjacent minterms (31) mountermy is called as an octet. An octet eliminates three variables from its groutland term.

adjacent, if their binary equivalent values are having only a one bit position change.

Because, the binary equivalent for o's 2' are having a charge only in one bit position

0:0000, 2=0010, only 2nd LSB bit is getting changed

No profession

## Minimal sop form: (B) simplified . Sop form:

To get the simplified expression in sop formue have to follow the steps below

- 1) Plot the K-map of place i's in the cells corresponding to the given manterms in the given Boolean expression.

- 2) check for the is a encircle those is which are not adjacent to any other 1's. There are called as isolated is

- so check for the i's which agree adjacent to only one i' and encircle them of a pair.

- 4) Check for the 1's that one having 4-adjacent is (appad) & 8 adjacent is (octet), even if some of the i's among them are already craincled. While doing this make sure that there are leng number of groups.

- 5) Form the simplified Boolean function by Summing all the product terms of all groups.

problems: simplify the following two variable Boolean functions in sop using k-map.

- 1) f(x,y) = \(\int m(0,1,3) 2) f(A,B) = \(\int m(1,2,3)\)

- 3) f(A,B) = Zm(1,3) 4) f(x,y) = Zm(0,1,2,3)

sol: 1) Gaven Boolean function 1 (+ 17 (2) 2 m (0,1,3)

simplified sop form is obtained by summing each term of each group f(x,y) = x1+4

simplified sop form

3) Given Boolean function

simplified sor from 15 P(A, B) = B

f(x,y) = 1 = m (0,1,2,3)

an a K-map, if every cell covers a minterm for the given Boolean function, the function will be equal to writt, 1-6, P(x, y) = 1

## 2) Given Boolean function

#### 3) Griven

$$F(A, B, c) = \sum m(0,1,2,3,4,5,6,7)$$

$A = \begin{cases} 0 & 0 & 1 \\ 0 & 1 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1 \end{cases}$

$A = \begin{cases} 0 & 0 \\ 0 & 1$

Irrespective of number of variables, if a K-map contains all 1's, the simpliful function value is unity.

= 4121 + 421 = 21 4 T, XYZ+XYZ x1421+x142 = XY . F(x, 4,2) 2 x 41+x4+21 5) Guven F(A, B,c) = A'B + A'C + B'C + ABC Given function is not in Cannonial form, convert into mintern Caronical form. = A'B(C+C') + A'(B+B')C+(A+A')BC + ABC = A'BC+A'BC'+A'BC+A'B'C+ABC+A'B'C = A'BC + A'B'C + ABC + A'BC'+ AB'C = m3 + m2 + m, + m5 + m7 E Zm (1,2,3,5,7) -I A (BC+BC')

> A.A' (B'C+BC) . +(A,B,c) = AB+C AAC = C

6) Gaven F(A, B,C) = Im (1,2,4,5,6,7)

Practis Problem:

simplify Boolean function in to sop using k-map

- 1) F(A,B,C): AB+AC+ABC 2) F(X,Y,2): Zm(0,2,3,4,6,7)

- 3) F(A, B, C) = TIM(2,3,4,5) u) F(A, B, C) = 5m (0,2,4,5,7)

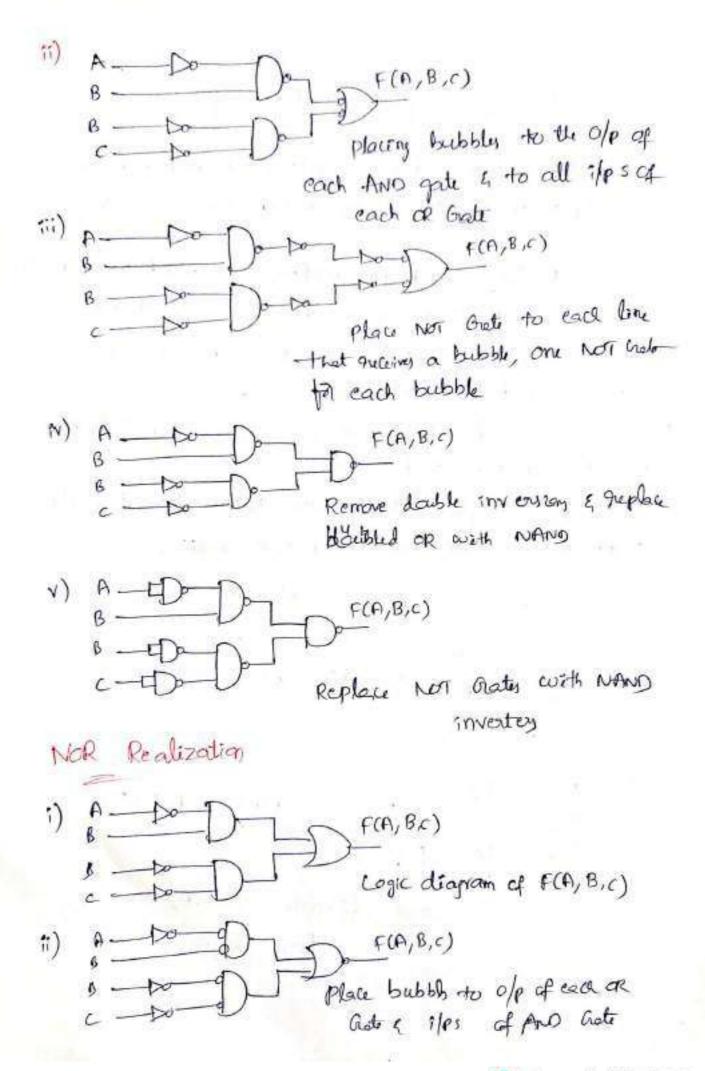

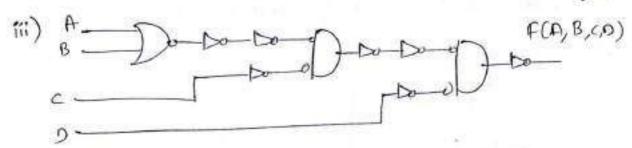

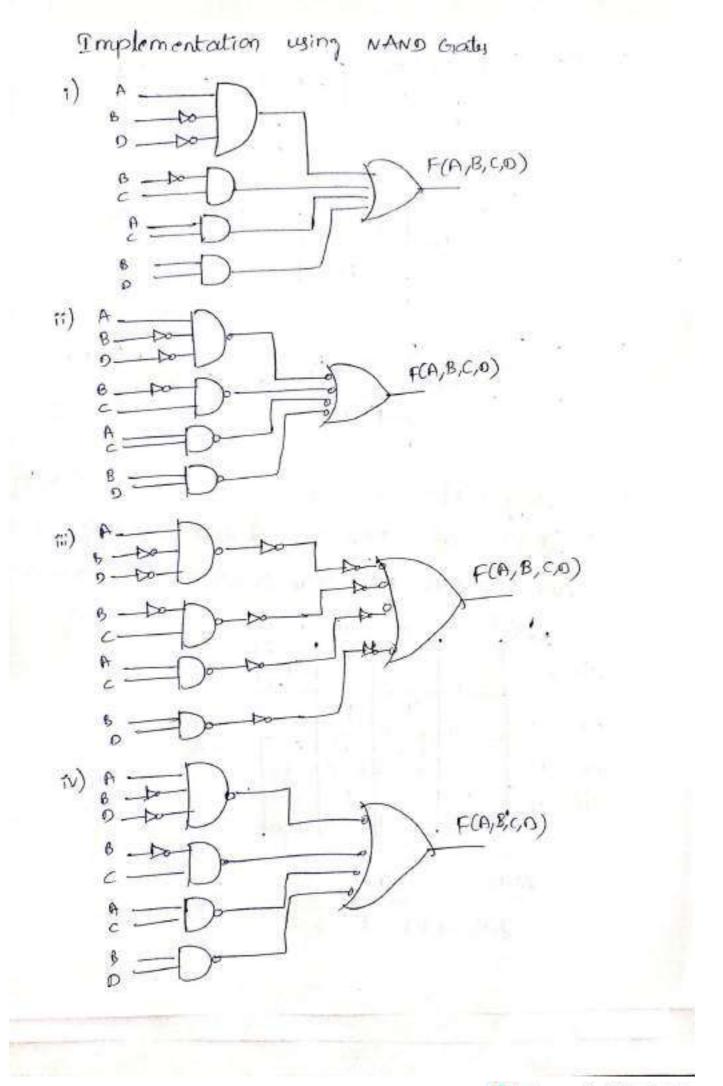

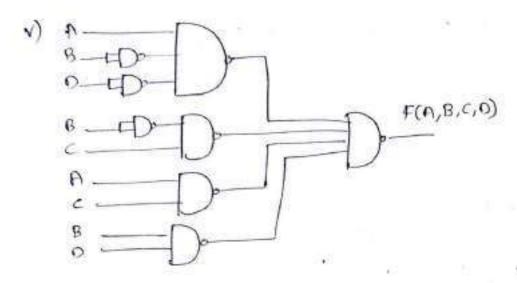

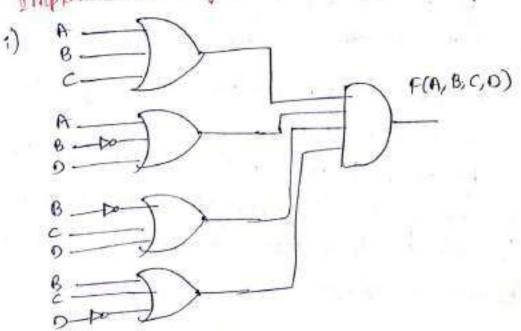

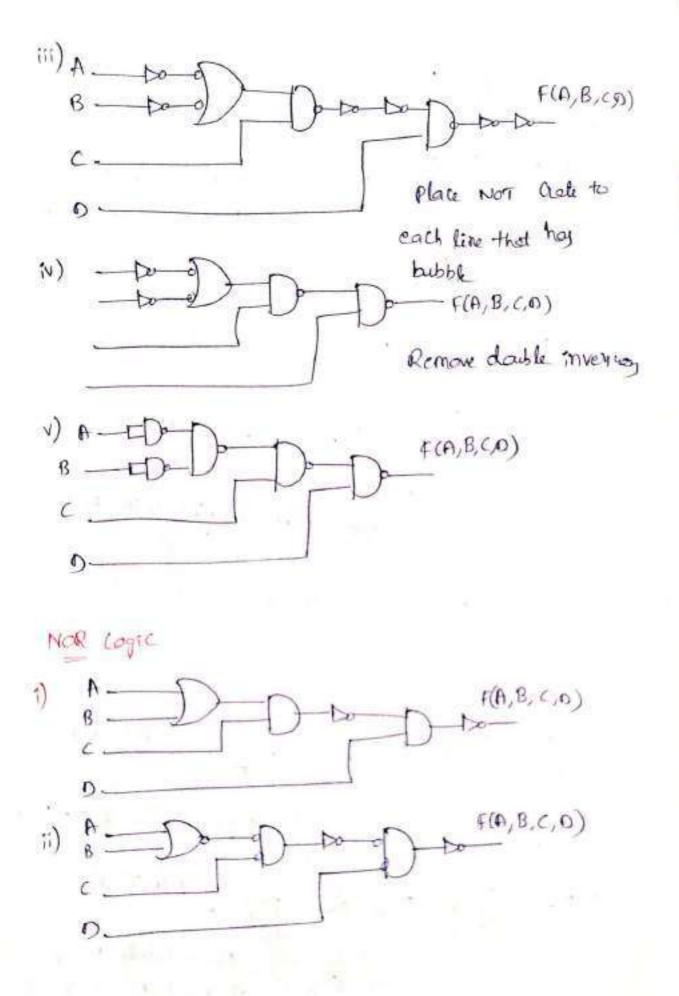

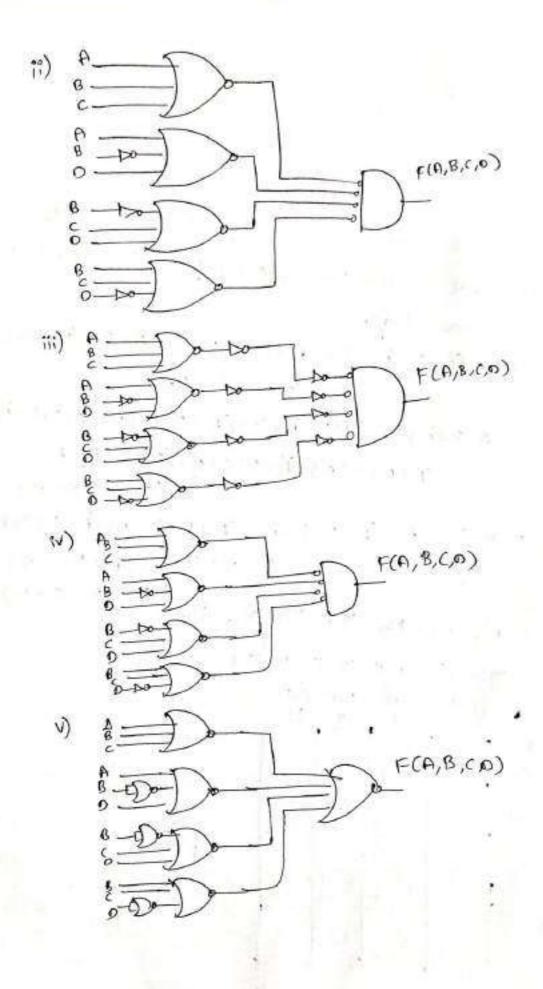

## NAND & NOR Implementation on NANDE wer healization;

1) Draw the Logic Diagram using bosic logic gates (AND, OR,

The output of the AND gates and to the inputs of or gates.

3) of NOR logic is being implemented, add bubble, to the cutput of OR Grates is to the input of the AND Grates

4) Add an inventer (Not Gate) to coch line that greceives a bubble in step 2 31 step 3

5) Eliminate double inversions of neplace bubbled AND by NOR, bubbled OR by NAND.

6) Replace single inventer with NAND inventer (in NAND inventer (i

Eq: Implement F(A,B,C): A'B+B'c' using NANO,

NOR logic gate.

sol: Guven F(A, B, c) = A'B+B'c'

NANO Realization:

B to D F(A, B, c) & A'B+8'c!

B to D Cogic diagram of F(A, B, c) cying

basic logic gates.

are stated to

The second second

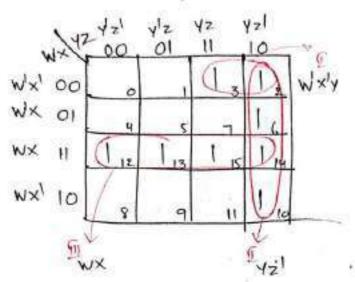

Q) simplify f(A,B,C,O) = \( m (2,3,5,7,8,10,11,13,14,15) in sop from cusing k-map of implement with NANO Chates.

Given f(A, B,C,D) = \( \int m (2,3,5,7,8,10,11,13,14,15) A'B' 00 01

AB - fill AC 11 -AB -AB 10 ABO

. . f(A,B,GO) = AB'0+Bc+Ac+BD

Practise problem:

Emplement NANO Logic for the simplified sop tom 1) F(A,B,C,O) = TIM (5,9, 11, 12, 13, 14, 15). Use K-map method 11) Y (WXY,Z) = 91 M (0,1,3,5,6,7,10,14,15) using K-nexp

## Minimal pos form on simplified pos form.

1) Plot the K-map & place ds in the place of marterms that owne given in the given Boolean expression, 2) check for the ols and encincle those ds that are not adjacent to any other os . There are called or isolated 3) check for the os which one adjacent to only one o' & encincle them as a pair u) check for quady (4 adjacent os) & octety (8 adjacentos) even if some of the o's among them one already encircled. While doing this, make scare—that there one hen rumba of groups.

product of all sum-terms of all groups.

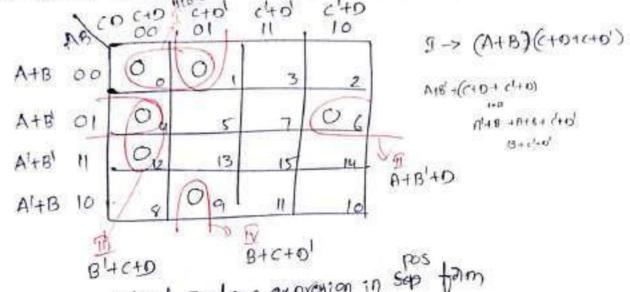

Eq. F(A, B, C, O) = If M(O, 1, 11, 6, 9, 12), simplify this function into pos from using k-map & implement

using NOR Books .

sol: Given F(A, B, C, O) = 9TM (0, 1, 4, 6, 9, 12)

· Simplified Boolean expression in sep form

(A+B+c) (A+B+0) · (B+C+0) (B+C+0)

Implementation using NOR Gody.

01+ 0

A+B 10

(2) Simplify the following Radown functions into sop using

1) f(A,B,C,O): \(\sigm(2,4,5,4)\), (2,13,14) 2) f (A,B,C,O): \(\sigm(0,1,3,7,0)\), (3,14,15)

3) F(w,x,4,2) = Zm(2,3,6,10,12,13,14,15)

1) f (A, B, C, O) = 7 m (3, 4, 5, 7, 9, 13, 14, 15)

5) F = 2m (1,2,4,6,7,11,12,14) 6) F(W,X,Y,2)= 2m(0,1,3,7,11,13,14,

1) Sel: Given P(A, B, C, O): Zm (2,4,5,9,11,12,13,14)

AB (0) OO OI II 10

AB (0) OO OI II 10

AB (1) D: D: D: AB (1)

AB (1) B (9) II 10

AB (1) B (9) II 10

... F(A,B,C,D) = A'B'CD' + ABD+ AB'D+BC

2) Gaven FCA, B, C, 0) = Zm(0,1,3,7,11,13,14,15) 18/c0 c's1 00 c'o AB'ch 10 A89 A18 00 A8 01 AB. 11 12 PB 10 A'B'c + ABO+ ABC + CD

Note: Sometime, the given Boolean function may not have variable. In that Ou, the desired alphabets can be taken as variables but he number of variables is to be decided board on higher number decimal equivalent.

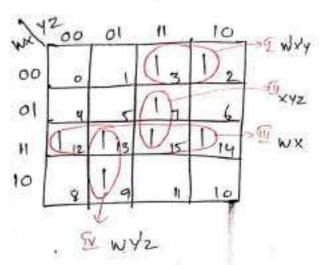

3) Gaven F(W,X,Y,Z) = Zm(2,3,6,10,12,13,14,15)

.. = wx + wx y + yz .

6) Gaven F(W,x,4,2) = Zm(2,3,7,9,12,13,14,15)

.. = Wy'z +WX+ XYZ+WXY

5) Ans: A'B'c'D+ AB'CD+ A'CD'+ A'BC+ BD'

4) -Ans: A' CO+ A'BC+ ABC+ AC'O

practise problems: simplify into sop curry k-map

1) Y(A, B, C,O) = A'B'C O'+ A'BC'O'+ A'BC'O+ ABC'O'+

ABC'O+ AB'C'O

9) F(W,X,Y,Z) = TIM (0,2,3,7,8,9,10,11)

prime Implicanti & Essential prime implicanti:

A prime implicant is a product term that is obtained by combining maximum number of possible adjacent minterns as a group in the K-map.

If a mintern is covered only one time in a prime implicant, then that prime implicant is said to be as essential prime implicant.

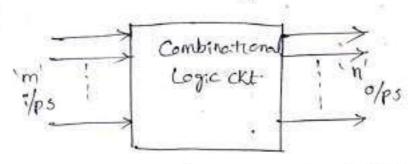

#### Combinational carriety

A Combinational circuit is the type of digital logic in which output depends only on the present input combination.

The logic gates are the building blacks to designing a combinational circuit. These circuit may have multiple outputs or single output.

Fig. shows the black representation of a Combinational

The various types of combinational logic blocks

that performs addition such as half adder, Full adder.

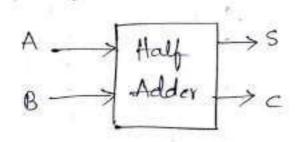

Half Adder A Half Adder is a type of arithmetic

logic circuit that adds two binary bits. It produce

the results sum(s) & Carry (c) at the output.

Block diagram of Half Adder

|   | 57  | ruth | r.ta | ble       |      |

|---|-----|------|------|-----------|------|

| ( | Cry | ut   |      | ou        | tout |

|   |     | 8    |      | $\subset$ | S    |

|   | 0   | 0    |      | 0         | 0    |

|   | 0   | 1    |      | 0         | 1    |

|   | 1   | 0    |      | 0         | 1    |

|   | l   | - (  |      | 1         | 0    |

The logic expressions of sum (s), carry (c) are S = A @ B = AB+ A B C = A.B

The logic gate implementation of half adder is the combination of a xor' gate for sum & on -AND gate for Carry out puts.

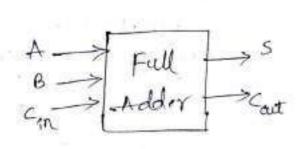

Full Adder

A full Adder is a type of contithmetic Circuit that adds three binary bits. It produces result Sum (5) & coop (Cout) at the output.

| 5  | Trat  | x -   | table |     |

|----|-------|-------|-------|-----|

|    | put   |       | outp  | utj |

| -A | Wan 8 | Cin . | Cout  | - S |

| 0  | 0     | 0     | 0.    | 0   |

| 0  | 0     |       | 0     | 1   |

| 0  | - 1   | 0     | 0     | 1   |

| 0  | 1     | 1 .   | 1     | 0   |

|    | 0     | 0     | 0     | 1   |

| 1  | 0     | 1     | 1     | 0   |

| 1  | (     | 0     | 1     | 0   |

| 1  | (     | 1     | 1     | 1   |

The Sum (s), Carry (Caut) are given below. S = Z (m1, m8, mu, m7) Cout = \( \( \text{m}\_3, \text{m}\_5, \text{m}\_6, \text{m}\_7 \) The simplified expressions are S= Cn ABB Cout = Gn. (A+B) + A-B.

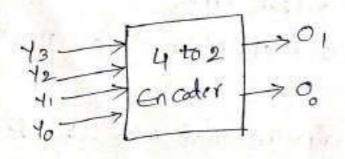

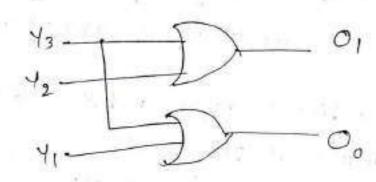

Encoders

-An encoder is a type of Combinational Circuit that produces the binary equivalent to the It has an input lines & defines n-bit code for the binary information at the output. sit can be represented as 27:n encoder. only one mput is activated at a time. The black diagram of use encoder is shown

the first that the second of the second probability

-Truth table

The Boolean expression to encoder is O, = Y2+43 O = Y1+Y3

## Logic circuit

Decoders

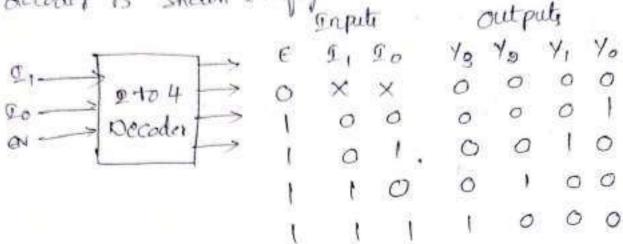

A decoder is a type of Combinational Logic Circuit that decody the binony infamation on 'n' lines to en output lines. It can be represented as n to . 27 37 n:27 decoder.

A decoder can also be used with Enable (E) signal. When enable is HIGH, then It provide

the outputs according to binary input information.

The block diagram and truth table of 2:4

decoder is sharn in fig.

The Boolean expressions for the outputs one

Multiplexers

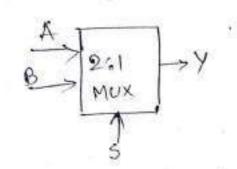

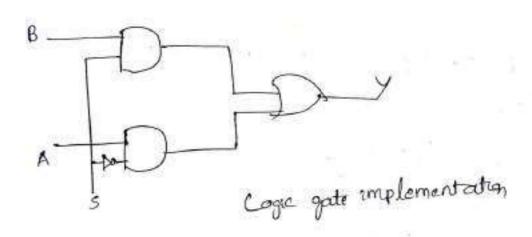

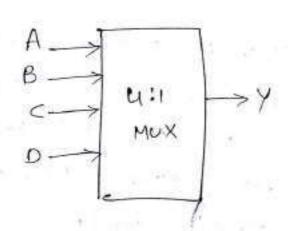

The term 'Multipler' means 'many to one'. It is a type of combinational circuit which has multiple input lines and one output line. It is also known as data selector at Mux 5 represented as 2n:1 multiplexer, where 'n' is the number of select lines, 2n is the number of input lines and '1' o/p line.

The types of multiplexers one 2:1 Mox, 4:1 Mux, 8:1 Mux aind so on.

The block diagram of 2 to 1 Multipletor

4 to 1 Multiplan

muth Hable

Y= 51 50. A+ 51.50 B+ S1.50 C+S1.500

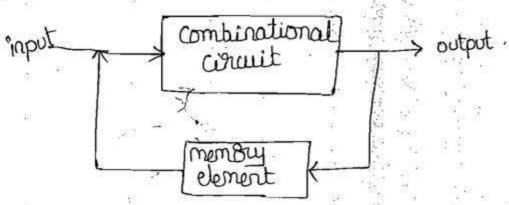

sequential circuits I.

In sequential logic circuits, the output is a function of the present inputs as well as the past inputs and outputs. sequential circuit include membry element to Store the past data. The flip-flop is a basic element of sequential logic circuits.

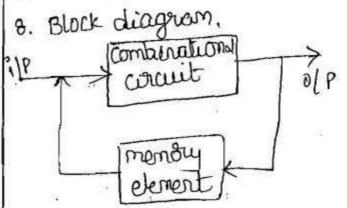

Block diagram of sequential circuit.

There are two types of sequential circuits.

- Synchronous circuit; The sequential circuits which are controlled by a clock are called synchronous sequential circuits. These circuits get actuated only clock signal is present.

- → A Synchronous circuit: The sequential circuits which are not controlled by a clock are called a synchronous sequential circuits, that is the sequential circuits in which events can take place any time the inputs are applied are called A synchronous sequential circuits.

# Comparison between synchronous & Asynchronous sequential of

- In Synchronous circuits, the charge in input signals can affect members elements upon activation of clock signal.

- a. In Synchronous circuits, membry elements are clocked FF's

- 3. The maximum operating speed of clock depends on time delays involved.

- 4. They are easien to design

- I In asynchronous circuits, change in input signals can affect membry elements at any instant of time.

- a. In a synchronous circuits, memory elements are either unclocked FFS or time delay elements.

- 3. Since the clock is not present, a synchronous circuits can operate faster than synchronous circuits.

- 4. more difficult to design.

## > latches & Flep flops; -

- > The most impostant membry element is the flip-flop which is made up of an assembly of logic gates.

- even though a logic gate by itself has no storage capability, several logic gates can be connected together in ways that permit information to be stored.

- -> Flip-flops are the basic building blocks of most sequential circuits. Actually, flip-flops is an one-built

- mendry device and it can store either 1800.

- -> latch is a sequential device that checks all its inputs continuously and changes its outputs accordingly at any time independent of a clock signal.

- → It refers to non-clocked flip-flops, because these flip flops 'latch on' to a 181 a o immediately upon receiving the input pulse.

> sifference between latches & flip flops.

#### latch

# 1. A latch is an electronic sequential logic concent used to stole information in an asynchronous avargement.

- a. one latch can store one but information, but output state changes only in response to data input

- 3. latch is an asynchronous device and it has no clock input.

- it remains constant until new inputs force it to change.

- 5. latches are level -sersitive and the output tracks the input when the level is high. Therefore as long as the level is logic level, the output can change if the input changes.

### Plip-flop.

- 1. A flip flop is an electronic sequential togic contait used to store information in an asynchronous avangement.

- a one flip-flop can store one but-data, but output state changes with clock pulse only.

- 3. Flip-flop has clock input and its output is synchronised with clock pulse.

- 4. Flip flops holds a trit value and it remains constant until a clock pulse is received.

- They can store the input only when there is either a rissing of falling edge of the clock.

## Difference between combinational, sequential circuits.

#### combinational circuit

- 1. The digital logic concuit whose outputs can be determined using the logic function of current state input are combinational logic concuits.

- 2. It contains no membry element

- 3. It's tehalicour is described by the set of output functions.

- 4. The combinational logic circuits are independent of the clocks.

- 5. The combinational digital logic circuit don't require any feed back.

- 6. combinational circuits are easy to design

- 7. Combinational counts are 7. Sequent taster because the delay slower to tetucen the input and the output concerts. Is due to propagation delay of 8. Block gates only.

8. Block diagram

- if Scombination Colp's

#### Sequential concuits.

- outputs can be determined unity

the logic function of current

state inputs and past state inputs

ore called as sequential logic

circuits.

- 2. It contains memory elements.

- 3. It's behaviour is described by the set of next state functions and the set of output functions.

- 4. The maximum sequential logic concerts are uses a clock for triggering the flip-flop operation

- 5. The Sequential digital logic circuits utilize the feedbacks from outputs to inputs.

- 6. Sequential concuits one complex to design.

- 7. Sequential circuits are slower than combinational circuits.

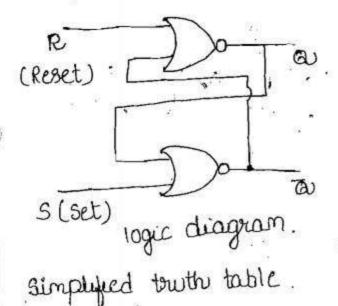

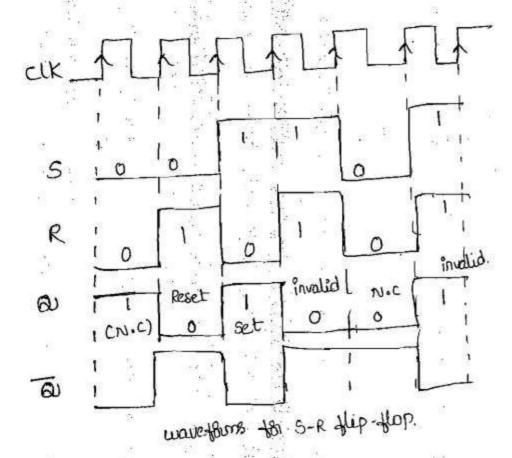

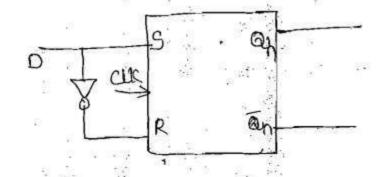

#### 5-R latch :-

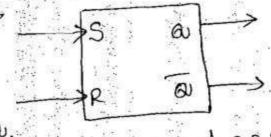

The S-R latch has two inputs, namely SET(S) and RESET(R), and two outputs a and a, where a is the complement of a.

where a is the wing NOR Grates; - [active-high S-R latch].

The logic diagram of the S-R latch composed of two USS-coupled NOR gates. Sand R are two inputs of 3-R latch.

- -> 5 Stands to set, it means that when 5 is 1, it stokes 1.

- > R Stands for Reset, and if R=1, Latch Reset and it's output will be 0. This comment is called as NOR gate latch & S-R latch.

| 5     | R     | anti | State   |

|-------|-------|------|---------|

| 0     | 0     | 0'n  | Marge   |

| 0     | 1 1 1 | 0    | Peret   |

| ı     | 0     | l:   | Set !   |

| 90 30 |       | 30.5 | invalid |

| 5   | R   | <b>a</b> n | anti | state        |

|-----|-----|------------|------|--------------|

| 0   | 0   | 0          | .0   | NO .         |

| 0   | 0   | 1:-        | . 1  | change       |

| 0   | 1   | 0          | 0    | RESET        |

| 0   |     | 1          | 0    |              |

| 1.7 | 0   | 0          | 1    | SET          |

| 1   | 0   | 15_        | 1    | , V          |

| 1   | 1 ' | 0          | X    | indetermined |

| L   |     | 11         | V    | (invalid).   |

|     | 1.  | 1,5        | . X  |              |

Touth table.

- NOR latch and it has no effect on the output state. a and a will remain in whatever state they were prior to the occurrence of this input condition.

- 2. SET = 0, RESET = 1, This will always seset a = 0, where it will semain even after RESET setwins to 0.

- 3. SET=1, RESET=0, This will always Set @=1, Where it will remain even after SET returns to 0.

- 4. SET = 1, RESET : 1. This condition tries to SET and Reset the latch at the same time, and it produces a = a = o . if the inpirare seturned to zero simultaneoulsly, the resulting output state is evaluate and impredictable. This input condition should so not be used. it is indetermined state or invalid state.

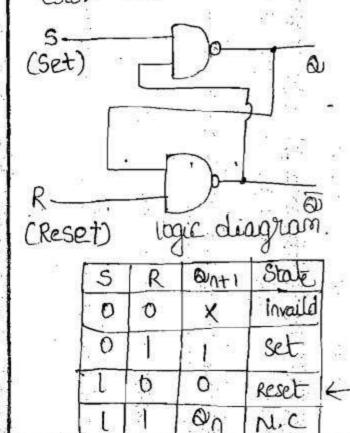

- 5-R latch using NAND Gates: (active www s-R latch)

- > The logic diagram of the 5-R latch composed of two coupled NAND gates.

| S        | R | On  | an+1  | state                     |

|----------|---|-----|-------|---------------------------|

| 0        | 0 | 0   | X     | indetermined<br>(invaild) |

| 0        | 0 |     | ×     | (INVOLUE)                 |

| 0        | 1 | 0   | 1     | Set .                     |

| 0        | 1 | 1   | 1     | 566                       |

| ı        | 0 | 0   | ٥     | Reset                     |

| ί        | 0 | 1   | ,O    |                           |

| ī        |   | 0   | 0     | . No. "                   |

| 1        |   |     | 1     | charige.                  |

| <u> </u> | 7 | wth | table |                           |

simplified truth table.

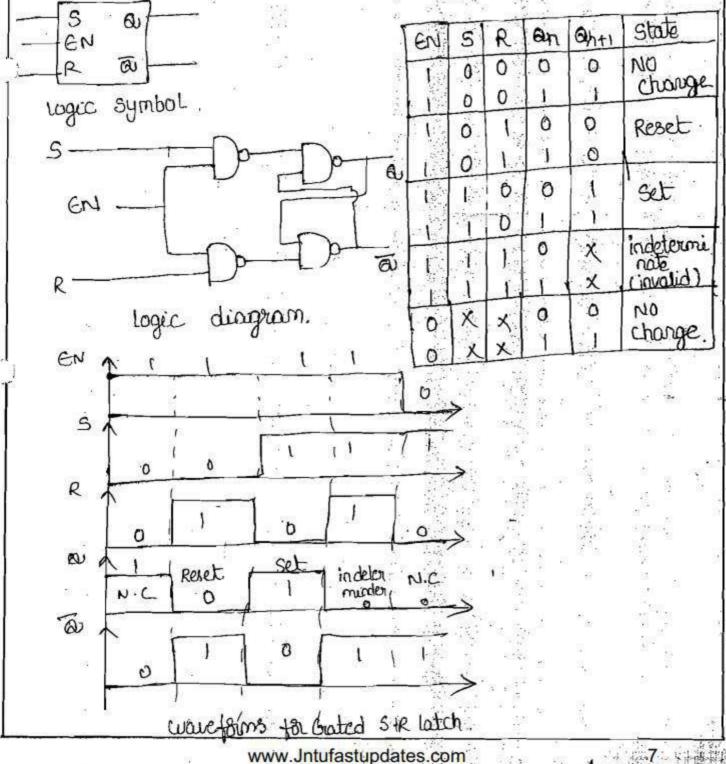

# \* Gated latches :-

The gated S-R latch: - The output can change state any time the input conditions are changed, so they are called Asynchrional latches. A goted S-R latch requires an Enable (EN) input. Its Sand & inputs will control the state of latch only when the Enable is high when the Enable is low, the inputs become ineffecture and no change of state can take place.

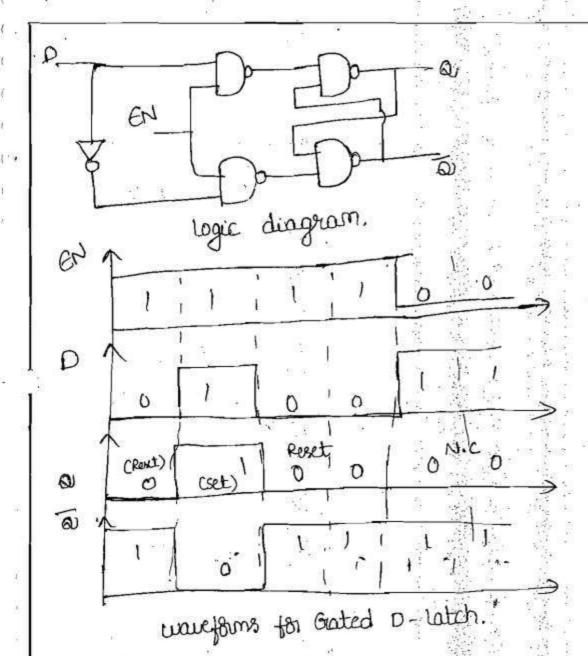

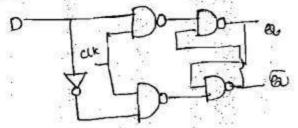

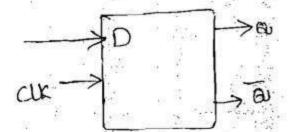

The Grated D-latch; - In many applications, it is not necessary to have separate sand R inputs to a latch. By the input combinations S=R=0 and S=R=1 are never needed, the sand R are always the complement of each other. so, to construct a latch with a single input (5) and obtain the R construct a latch with a single input is labelled D (the data). input by inventing it This single input is labelled D (the data).

when D=1, S=1 and R=0, causing the latch to set when Enabled. When D=0, S=0 and R=1, causing the latch to Reset when chabled. When En is low, the latch is ineffective, and when change in the value of D input does not affect the autput at

when EN is high, a low 0-input makes a low, i.e results the latch and high n input makes a a high, that is sets the latch.

Inter output a follows the D-input when EN is high. So this latch is said to be triansparent.

logic symbol 0 0 state (Unti 6m 0 0 0 Reset 0 0 set Touth table NO change 0 Ø (NC)

MARK ST

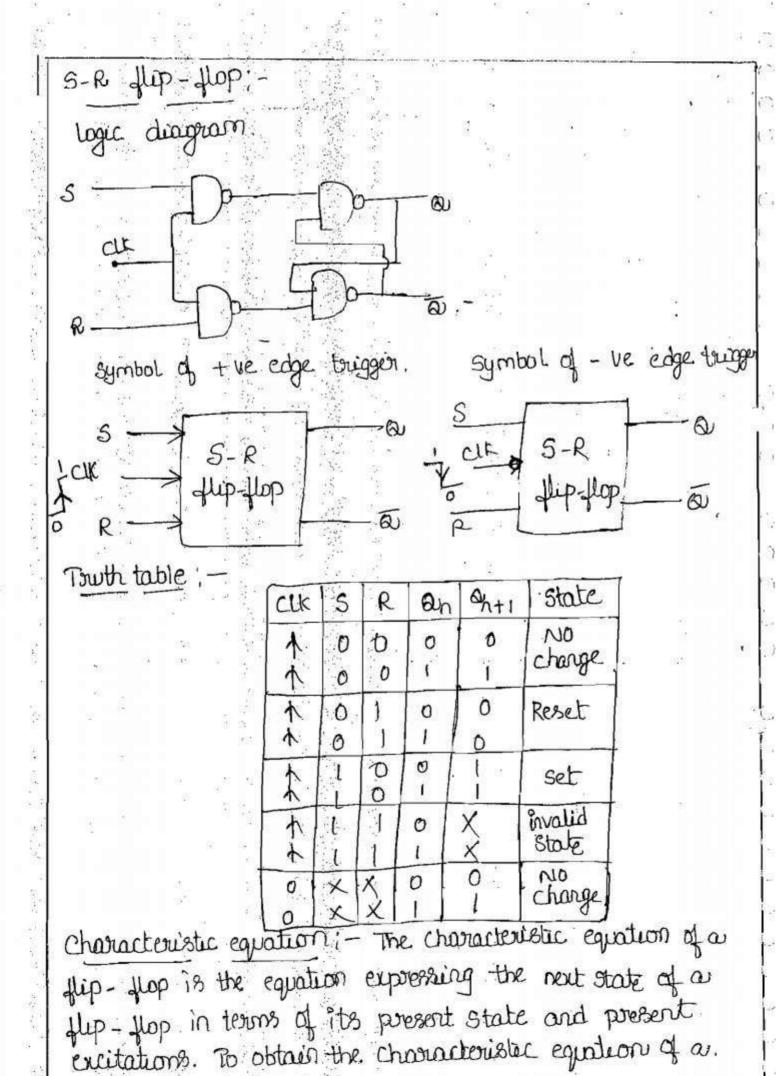

Flip-flops !-

Types of flip-flops;-

www.Jntufastupdates.com

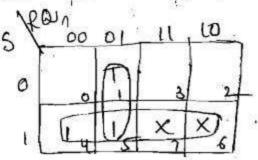

flip-flop write the excitation requirements of the flip-flop, draw a k-map for the next state of the flip-flop in terms of its present state and inputs and simplify it

ant1 = 3+ Ran

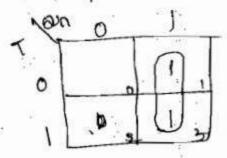

Powth sable: -

| S                         | R  | @nt] |

|---------------------------|----|------|

| 0                         | 0  | (B)n |

| 0                         | 11 | 0    |

| 1                         | 0  | 1    |

| $\lfloor \lfloor \rfloor$ |    | Χ    |

Excitation table: - A table which lists the present state, the next state and the excitations of a flip-flop is scalled the excitation table.

A table which indicates the excitations required to take the flip-flop from the present state to the next state.

| Present<br>State an | next state |   | wed<br>R |

|---------------------|------------|---|----------|

| 0                   | 0          | 0 | Χ        |

| 0                   | 1-         | 1 | O        |

| 1                   | 0          | 0 | 1        |

|                     | 1          | X | o]       |

Timing diagram:

logic diagram .

Symbol of the edge trugger symbol of the trugger

12

| <del> </del>               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

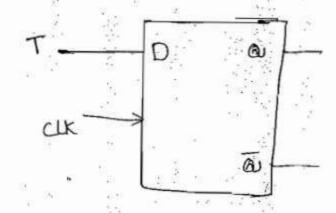

| . Towth table :-           | characteristic Table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CUK                        | D an ant 1 state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| D Qun+1                    | a 0 0 Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 100                        | 0 1 0 set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                            | i O Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1                          | x 0 0 NO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |